我們重視您的隱私

通過點擊「允許所有 Cookie」,代表您同意在您的設備上存儲 Cookie 以增強網站瀏覽體驗、分析網站使用情況並協助我們的行銷和網站效能優化工作。您可以在我們的隱私權政策中找到有關於此的更多資訊。

Winstar提供包括TN/STN LCD、OLED和TFT在內的數千種顯示器模組,而在這些顯示器模組中,有許多不同類型的介面可將圖像數據傳送到顯示器模組。客戶可能會問,哪個是最好的?或哪個可以滿足產品要求?本文針對顯示介面的數據傳輸議題進行探討。

顯示介面最主要的問題就是「通訊頻寬」,為什麼通訊頻寬會是主要問題?通訊頻寬表示在一通訊介面中,其數據傳輸量的衡量。所以,通訊頻寬會影響顯示器對資料的傳送/接收速率,進而影響顯示器的刷新率,也就是顯示器效能。

目前市面上廣為人知的顯示器介面有以下這些:

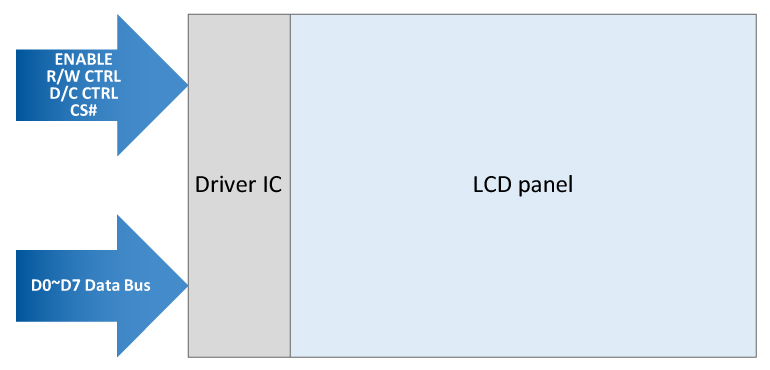

使用8位元資料匯流排,硬體架構需要8條資料線及3條控制線,所需要的引腳數較多。

當控制訊號啟動後,顯示資料便可透過資料線來傳送;而通訊頻寬取決於驅動IC 上的啟動運行速度。以QVGA 320×240 點陣式LCD為例,在IC訊號啟動後,通訊頻寬將為「320 × 240 ÷ 8位元(資料寬度) × 60 fps (frame per second) = 576KHz」。 優點:早期架構,控制簡單,無須時脈或同步訊號;功耗低,適合小尺寸顯示器產品。

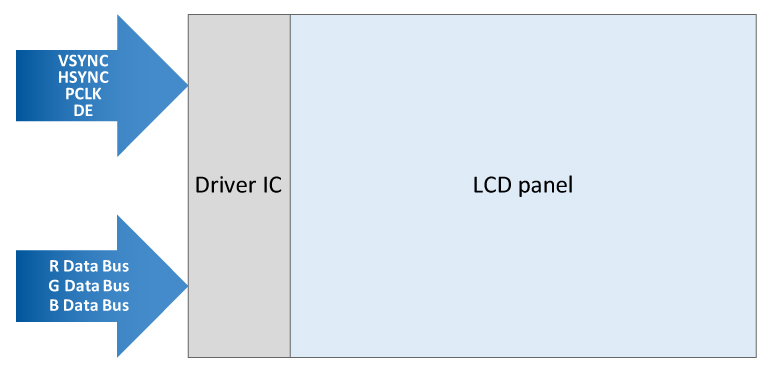

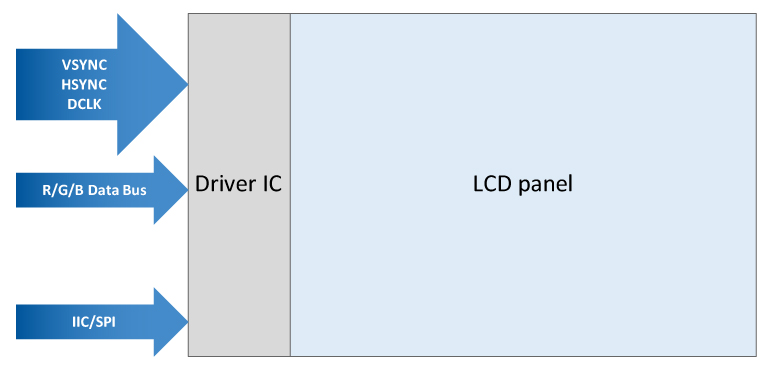

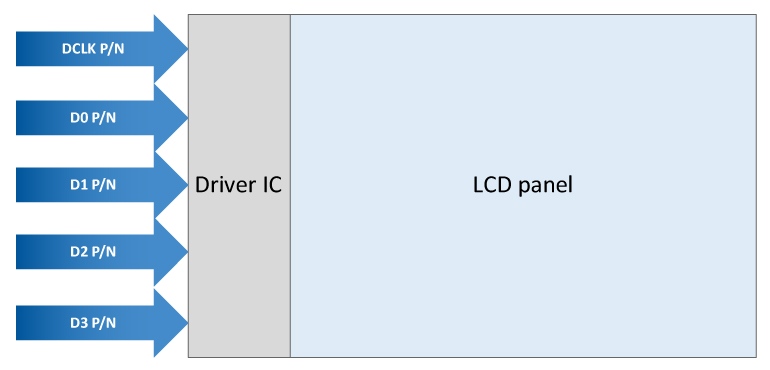

RGB介面就是透過並行方式,將驅動時序透過資料的輸入/輸出傳送到顯示器驅動IC,包括R/ G/ B資料、垂直同步訊號(V-SYNC, Vertical synchronizing signal)、水平同步訊號(H-SYNC, Horizontal synchronizing signal)、資料致能(DE, Data Enable)訊號,以及時脈訊號PCLK (Pixel Clock),RGB666的顯示介面如下:

顯示資料的傳送方式同1.1,但顯示器的解析度更高;以WVGA 800×480 (像素)為例,通訊頻寬為「800 × 480 × 60 fps (frame per second) = 23.04Mhz (畫素時脈)」 優點: 成本低廉但螢幕解析度受限於時脈訊號的頻率,且色彩深度越高則需要的實體接線數越多,適合小尺寸顯示器使用。

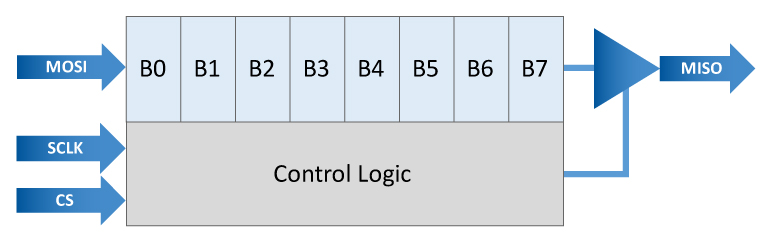

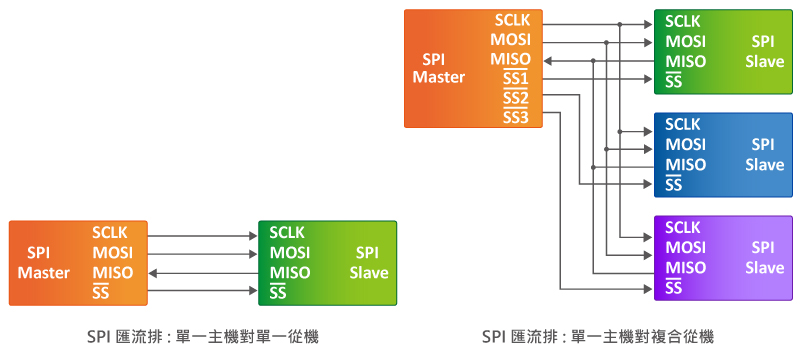

SPI為一主從式架構,通常有一個Master (主設備)和一個或多個Slave (從設備)。介面上共有4支接腳,對接方法及硬體結構如下:

接腳名稱及意義說明

MOSI (Master Output, Slave Input):主設備數據輸出、從設備數據輸入

MISO (Master Input, Slave Output):主設備數據輸入、從設備數據輸出

SCLK (Serial Clock):時脈信號,由主設備產生並控制

CS /SS (Chip Select/Slave Select):從設備選擇信號,由主設備控制;從設備只有在 CS信號為低電位時,才會對主設備的操作指令有反應

SPI介面下,顯示資料按順序傳送,以QVGA 320×240 (像素)為例,通訊頻寬為「320 × 240 × 16位元(色彩深度) × 30 fps (frame per second) = 36.864 Mhz」 優點--成本低廉: 結構簡單、引腳數少,適合字元型顯示器。

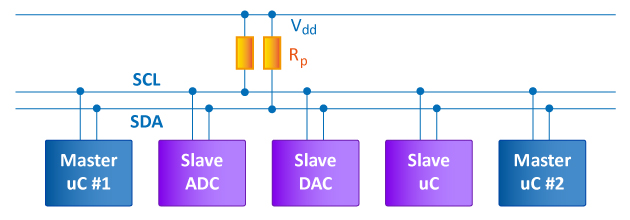

不同於SPI的點→點(或點→多點)結構,I²C以匯流排型式介接,同時排上允許多個主設備和多個從設備串連,介接方法及硬體結構如下:

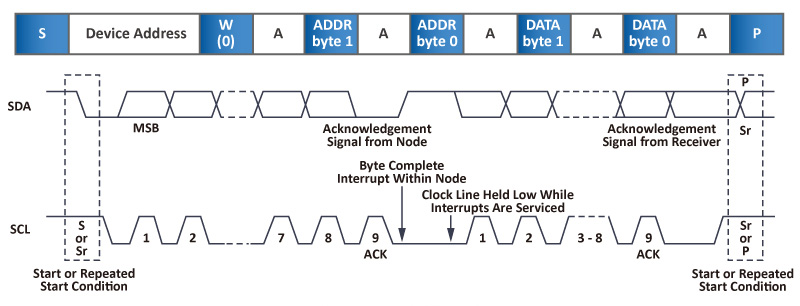

I²C的架構比SPI更簡單,只有兩條訊號線:資料線(SDA, Serial Data Line)及時脈線(SCL, Serial Clock Line),通訊頻寬如下:

Standard mode = 100K bit/s.

Full speed mode = 400K bit/s.

Fast mode = 1M bit/s.

High speed mode = 3.2M bit/s.

優點--成本低廉: 結構與引腳數都比SPI更簡單、更少,適合字元型顯示器。

顯示以 RGB 順序傳輸的數據。顯示介面的通訊頻寬為QVGA 320 * 240 (pixels) * 3 dot * 30 fps = 6912000 Hz (DCLK).

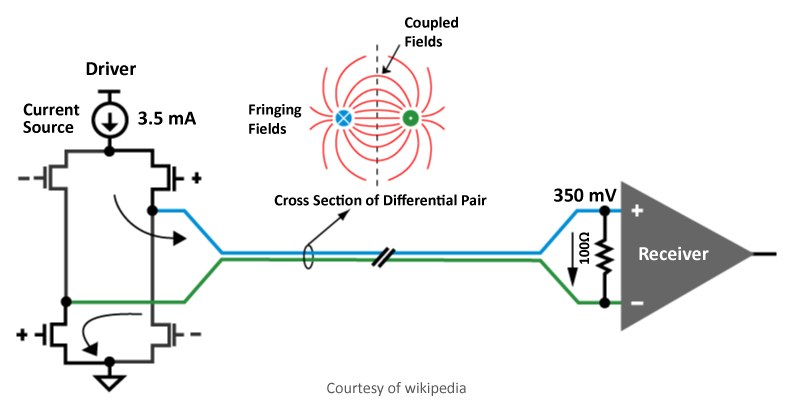

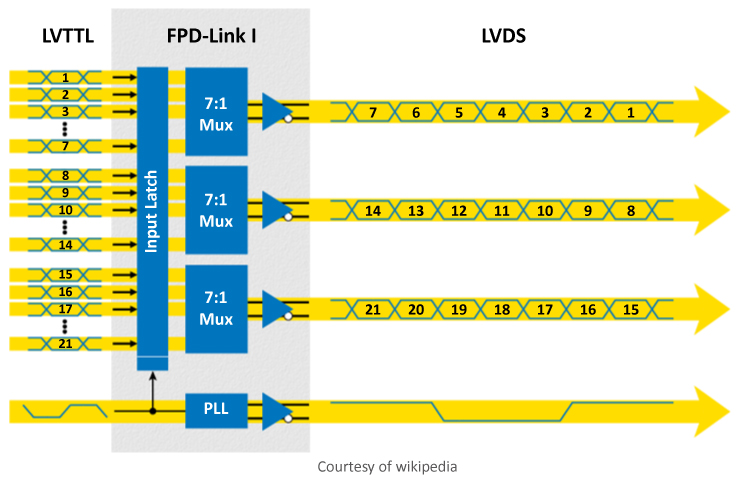

LVDS (Low voltage differential signaling)是在1994年推出的技術標準,LVDS規範了差分訊號與串聯訊號標準,但請注意它並不是一個通訊協定。LVDS能在低電壓下、以高訊訊號進行資料傳輸,且僅需透過一條便宜的雙絞銅線即可實現。

LVDS只是一物理層規範,並非韌體層的介面協定。在LVDS資料層上,有許多資料通訊標準和應用程序,並添加在開放式系統互聯(Open System Interconnection)模型中的資料鏈結層,例如FPD(Flat Panel Display)-Link,平板顯示鏈結。

在早期,筆記型電腦和LCD顯示器供應商在提及他們的通訊協議時,常誤使用「LVDS」而非「FPD-Link」,久而久之「LVDS」便錯誤地成為平板顯示鏈結中,影像顯示的工程詞彙同義字。

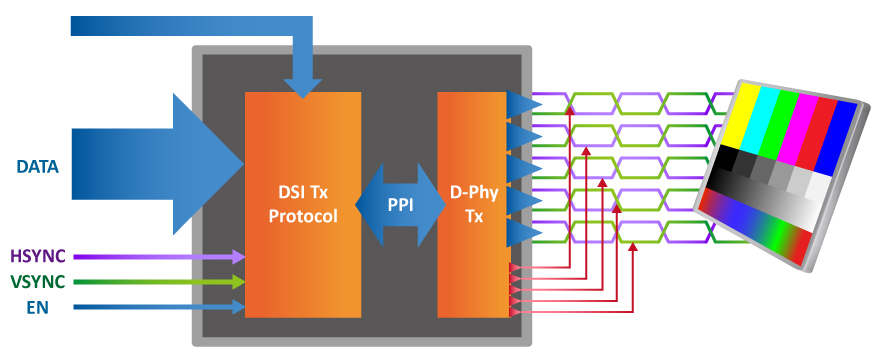

MIPI聯盟旨在降低行動設備中顯示控制器的成本,一般是針對LCD和類似的顯示技術。MIPI定義了主機、圖像數據訊號源,和目標設備之間的串聯總線及通訊協議。

DSI (Display Serial Interface, 顯示串列介面)定義高速物理層中,例如: 4.5Gbit/每秒/每通道的物理層(PHY, physical),其差分訊號點對點串聯總線。該總線包括一個高速時鐘通道和一個(或多個)數據通道。

總線上的圖像數據與水平、垂直間隔的信號交錯。為節省顯示器的暫存器,數據資料被即時傳輸到顯示器而非被儲存在設備中。然而這也意味著設備必須不斷刷新(以每秒30或60幀的速度),否則圖像將會遺失;圖像數據僅在HS模式(Horizontal-SYNC mode)下發送。在HS模式下,指令會在垂直區間傳輸。

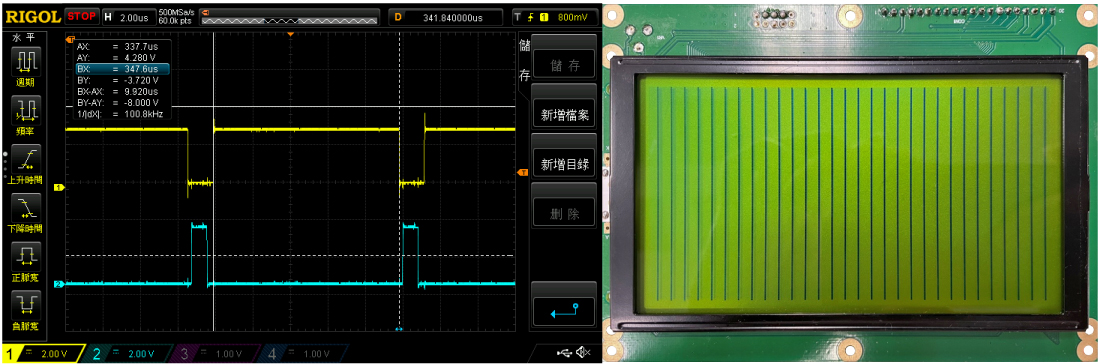

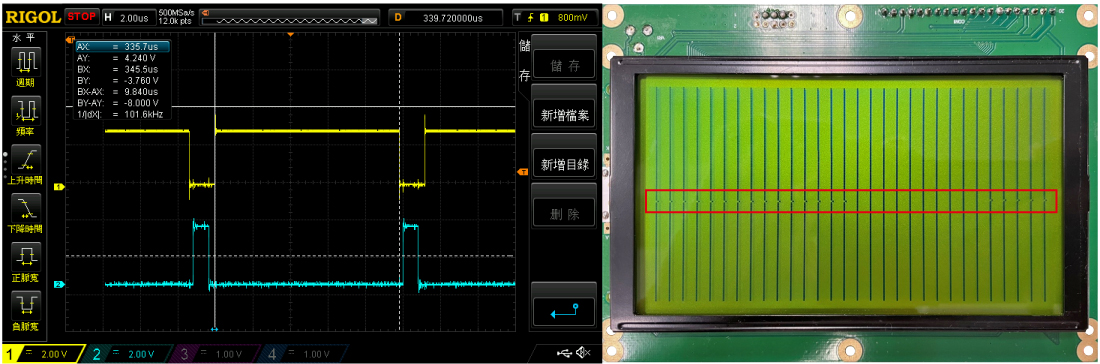

有一顆LCD控制器面臨停產,客戶希望可以設計一塊控制板可以腳位兼容。為了兼容介面我們硬體工程師設計一塊MCU介面的控制板。實驗結果ENABLE訊號至少需要9.92uS(如下圖Channel1),這意味著通訊頻寬最大約為100KBPS。

當我們將ENABLE時間縮短至9.84uS(通訊速率大約101KBPS),就會出現一些缺陷如下圖所示

談完這麼多顯示介面後,究竟是哪種介面最好呢?

其實,介面間並沒有所謂的最好或最不好,只有適合與不適合產品的應用;因此這邊提供以下表格,針對本文所介紹的各種介面,提供多面向的優劣勢分析,讓您能透過分析與比較來找出最適合自己產品的顯示介面!

| 顯示介面 | 解析度 | 傳輸速度 | 引腳數 | 雜訊 | 功耗 | 傳輸距離 | 成本 |

|---|---|---|---|---|---|---|---|

| 微控制器 8080/6800 | 中 | 低 | 較多 | 中等 | 低 | 短 | 低 |

| RGB 16/18/24 | 中 | 快 | 較多 | 最糟 | 高 | 短 | 低 |

| SPI | 小 | 低 | 較少 | 中等 | 低 | 短 | 低 |

| I²C | 小 | 低 | 較少 | 中等 | 低 | 短 | 低 |

| 串列 RGB 6/8 | 中 | 快 | 較少 | 最糟 | 高 | 短 | 低 |

| LVDS | 大 | 快 | 較少 | 最佳 | 低 | 長 | 高 |

| MIPI | 大 | 最快 | 較少 | 最佳 | 低 | 短 | 中 |

通過點擊「允許所有 Cookie」,代表您同意在您的設備上存儲 Cookie 以增強網站瀏覽體驗、分析網站使用情況並協助我們的行銷和網站效能優化工作。您可以在我們的隱私權政策中找到有關於此的更多資訊。