Prefácio:

A Winstar fornece milhares de módulos de display de modelos, incluídos TN/STN LCD, OLED e TFT. E existem muitos tipos de interface para fornecer os dados da imagem ao módulo de visualização. Os clientes podem se perguntar qual seria o melhor ou capaz de satisfazer a exigência. Este artigo discutirá um problema relativo à transferência dos dados das interfaces do display.

Uma questão significativa com a interface do display é a largura de banda de comunicação (BW). Por que a BW é uma questão? A BW representa a medição de transferência de dados no canal de comunicação. Assim, a BW afeta a resposta do display aos dados da tela, o que significa a taxa de atualização do display. O desempenho do display, em outras palavras.

Introdução:

Interfaces de display bem conhecidas atualmente:

1.Paralelas

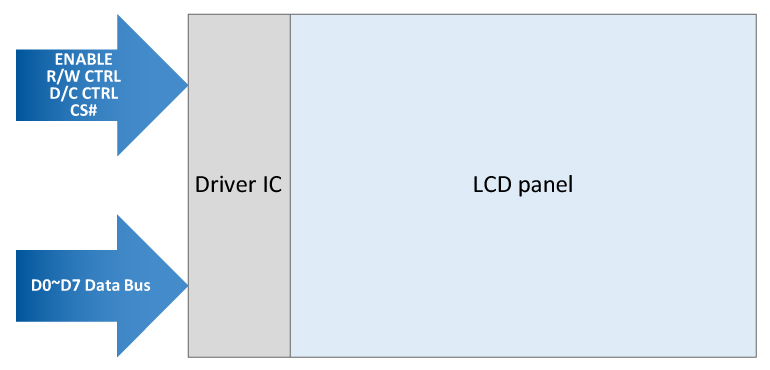

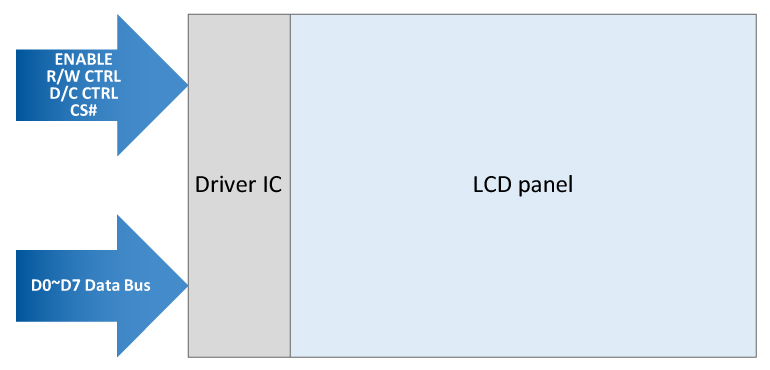

1-1 Interface MCU 8080/6800

Visualiza os dados brutos enviados pelo bus de dados de acordo com o sinal do bus de controle. A largura de banda de comunicação depende da habilitação da velocidade em execução no IC do Driver. LCD na matriz de pontos QVGA 320x240, ou seja, a largura de banda de comunicação será 320 * 240 / 8 bit (largura de dados) * 60 fps = 576KHz ao sinal HABILITAR.

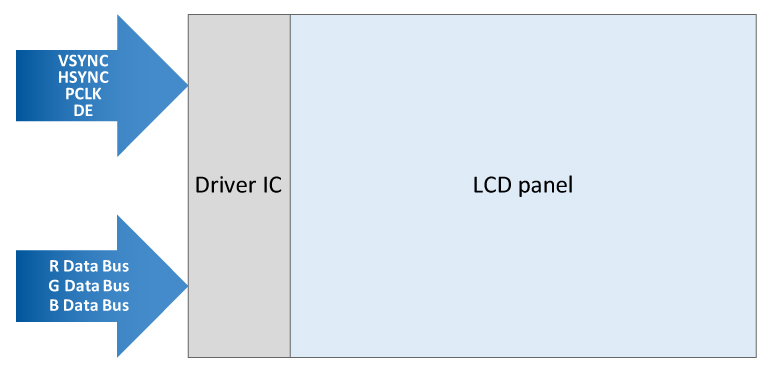

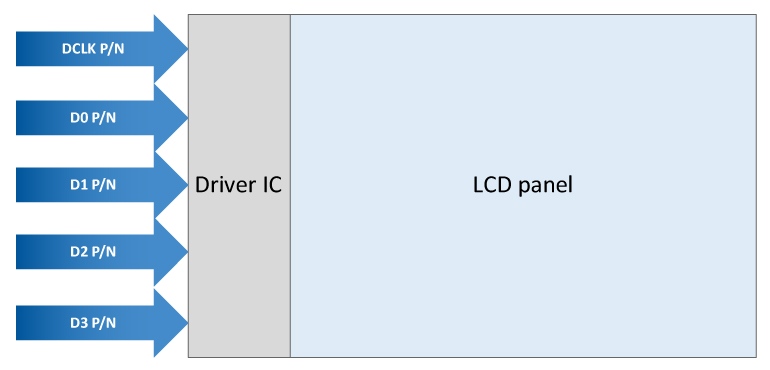

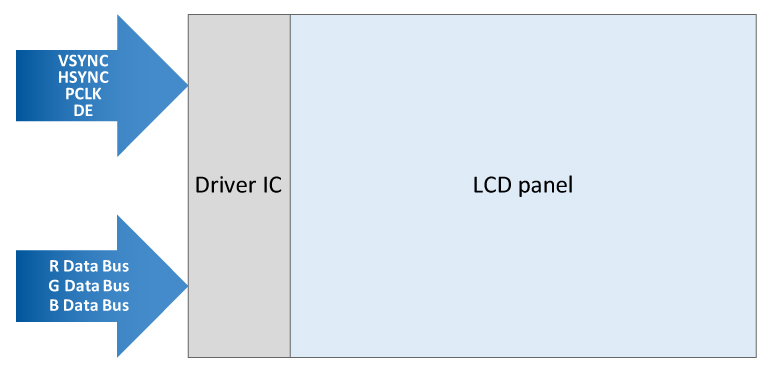

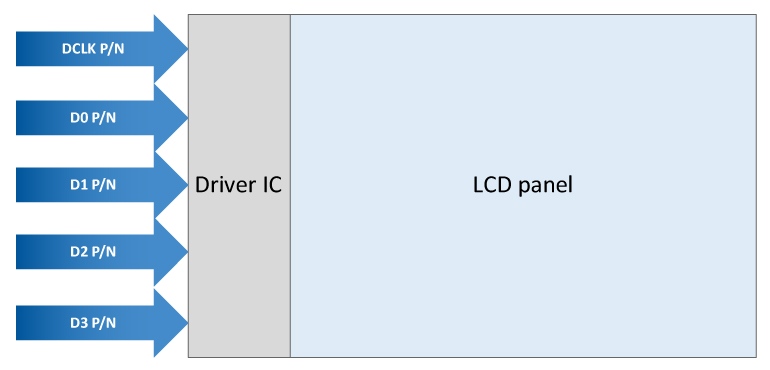

1.2 RGB paralelo 16/18/24 bits

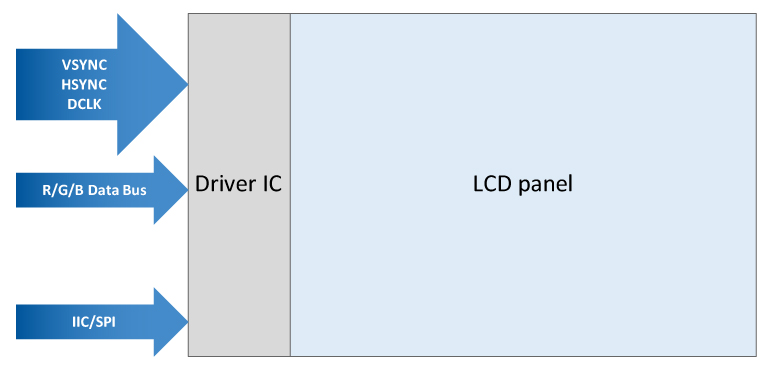

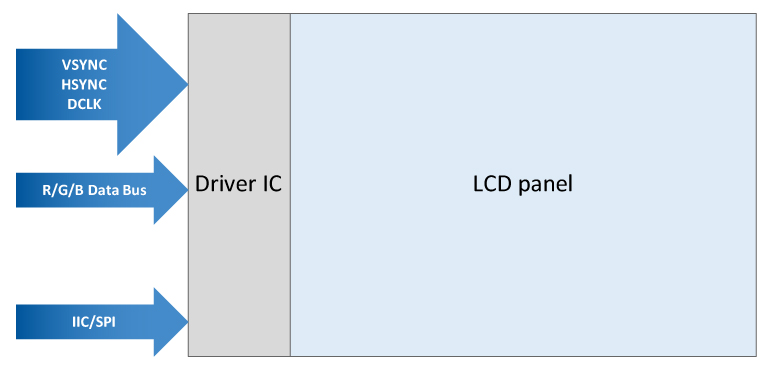

A interface RGB transmite a temporização da unidade ao IC do driver de display por meio do input/output de dados de modo paralelo, incluindo os dados R/G/B, sinal de sincronização vertical (V-SYNC, sinal de sincronização vertical), sinal de sincronização horizontal (H-SYNC, sinal de sincronização horizontal), sinal de habilitação de dados (DE, Habilitação de Dados) e sinal de clock PCLK (Pixel Clock). A interface do display de RGB666 é a seguinte:

Os dados brutos do display transferidos igual acima. Mas a resolução do display está se tornando cada vez mais alta, ou seja, WVGA 800 * 480 (pixels) * 60 fps = 23,04 MHz. (PCLK)

2.Serial

2.1 SPI (Interface Periférica Serial)

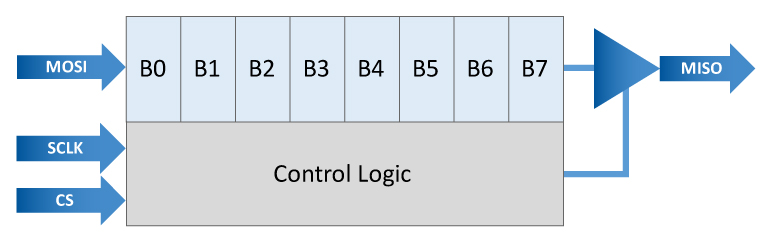

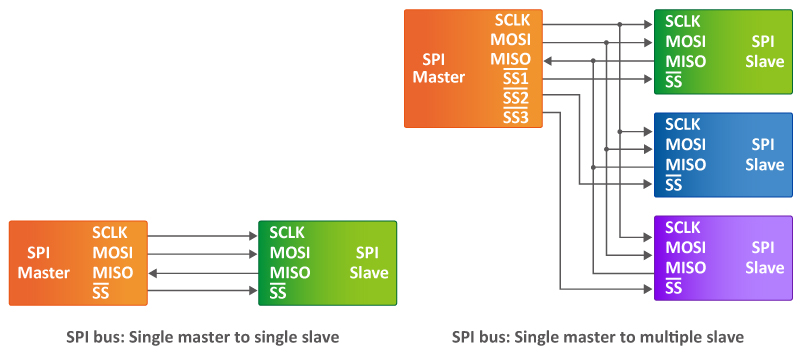

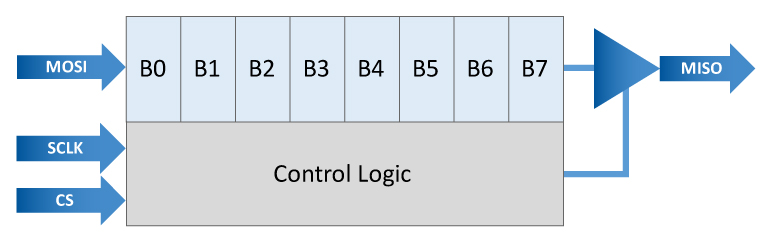

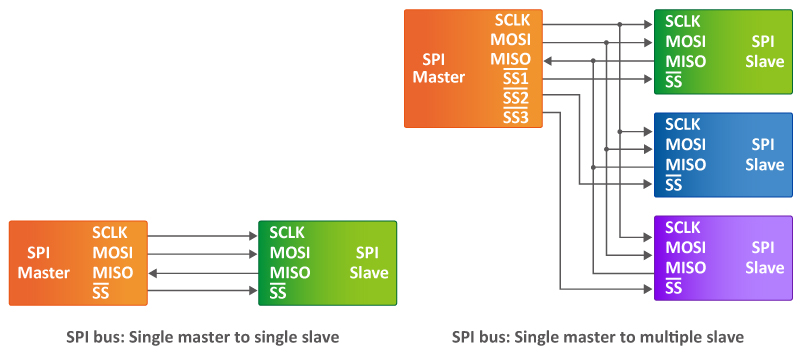

SPI é uma interface com base em master-slave, geralmente com um Master (dispositivo master) e um ou mais slaves (dispositivos slave). Existem 4 pins na interface. O método de conexão e a estrutura hardware são os seguintes:

[Estrutura da interface SPI]

SCLK: O clock síncrono utilizado por todos os dispositivos. O master aciona este clock os slaves recebem o clock.

MOSI: Saída Master, entrada slave. Esta é a linha de dados principal acionada pelo master a todos os slaves no bus SPI. Só o slave selecionado sincroniza os dados de MOSI.

MISO: Entrada Master, saída slave. Esta é a linha de dados principal acionados pelo slave selecionado para o master. Só o slave selecionado pode acionar este circuito. De fato, é o único circuito na disposição do bus SPI que um slave pode acionar realmente.

CS: Seleção do chip. Este sinal é único para cada slave. Quando está ativo, o slave selecionado deve acionar o MISO.

[Exemplo do esquema SPI]

Dados do display transferidos em sequência. Largura de banda de comunicação da interface do display, isto é, QVGA 320 * 240 (pixels) * 16 bit (profundidade da cor) * 30 fps = 36,864 MHz.

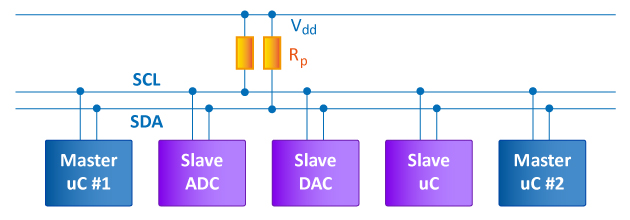

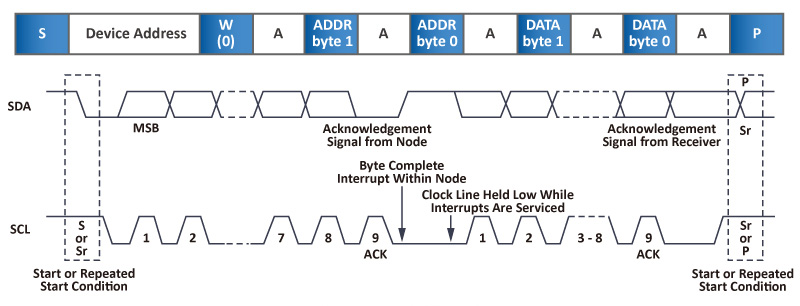

2.2 IIC (Circuito Inter-Integrado) ou conhecido alternativamente como I²C):

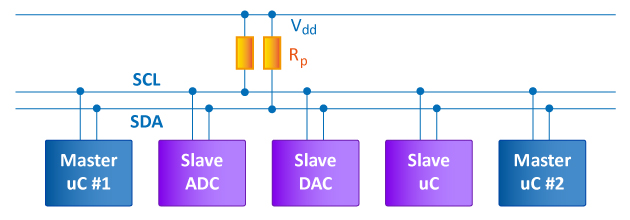

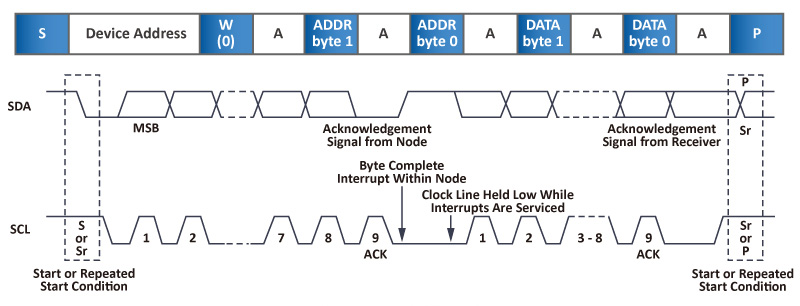

Diferente da base ponto a ponto (ou ponto-multipontos) do SPI, I²C é interfaceado na forma de um bus de dados, que permite ligar em série mais dispositivos master e mais dispositivos slave. O método de interface e a estrutura de hardware são os seguintes:

[I²C schematic]

[Cortesia do dispositivo analógico]

Standard mode = 100K bit/s.

Full speed mode = 400K bit/s.

Fast mode = 1M bit/s.

High speed mode = 3.2M bit/s.

2.3 Serial RGB 6/8 bits.

Dados de display transferidos em sequência RGB. Largura de banda de comunicação da interface do display, por ex., QVGA 320 * 240 (pixels) * 3 dot * 30 fps = 6912000 Hz (DCLK).

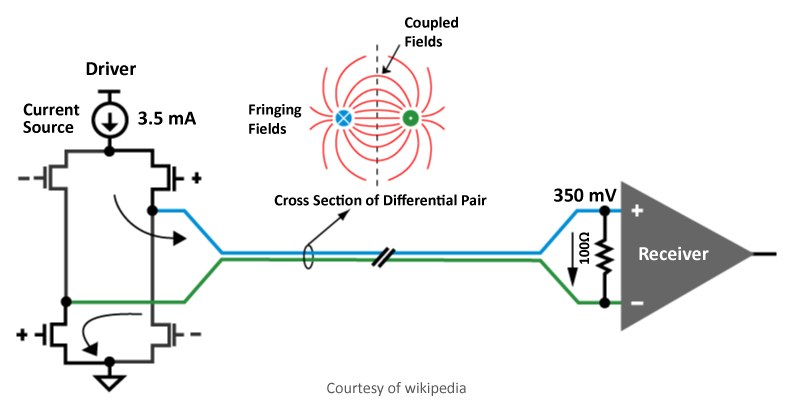

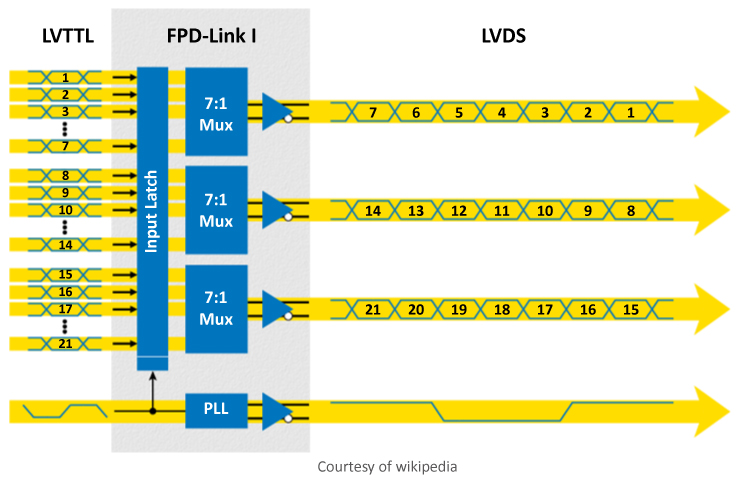

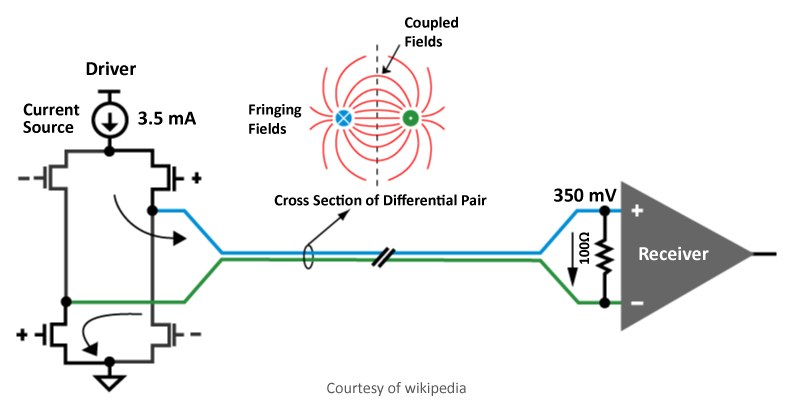

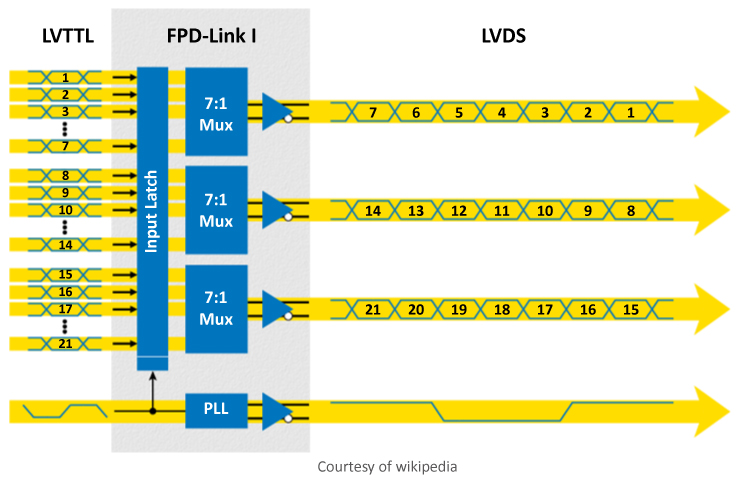

2.4 LVDS: Sinal diferencial de baixa tensão. Deveria chamar FPD-Link para a interface de display

LVDS é uma norma técnica inserida em 1994 que especifica as características elétricas de uma norma de sinalização serial, diferencial, mas não é um protocolo. LVDS é só uma especificação de nível físico; muitas normas e aplicações de comunicação de dados a utilizam e adicionam ainda um nível de conexão de dados como definido no modelo OSI. O LVDS opera à baixa potência e pode operar a velocidades muito altas utilizando cabos de cobre de par torcido de baixo custo.

No início, os fornecedores de notebooks e display LCD usavam geralmente LVDS, em vez de FPD-Link, quando se referiam ao seu protocolo. O termo LVDS tornou-se incorretamente sinônimo de Link de Display de Tela Plana no vocabulário de engenharia do vídeo de display.

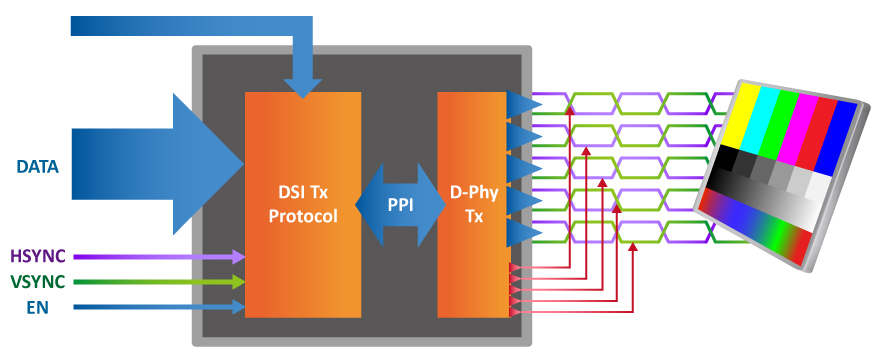

2.5 MIPI CSI/DSI: Interface do Processador do Setor Móvel.

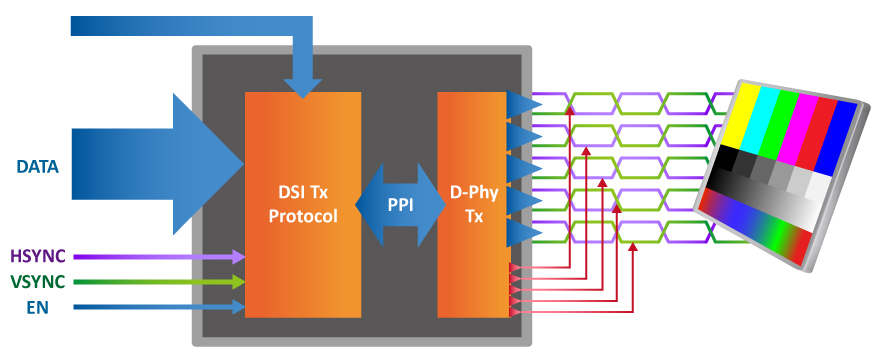

[Visão do display de DSI.]

MIPI Alliance almejava reduzir o custo dos controladores de display em dispositivos móveis. Ele define um bus serial e um protocolo de comunicação entre o host, a fonte dos dados de imagem e o dispositivo de destino. É o objetivo esperado para o LCD e tecnologias de display similares.

[Visão do sistema de DSI.]

O DSI especifica um bus serial ponto a ponto de sinalização diferencial em alta velocidade (por ex., 4,5 Gbit/s/faixa para D-PHY 2.0). Este bus inclui ma faixa de clock de alta velocidade e uma ou mais faixas de dados.

Os dados da imagem no bus são interligados com sinais de intervalos de vazios horizontais e verticais. Os dados são transferidos para o display em tempo real e não armazenados pelo dispositivo para salvar a memória de vídeo no display. Entretanto, significa também que o dispositivo deve ser continuamente atualizado (a uma velocidade de 30 ou 60 quadros por segundo) ou perder a imagem. Os dados da imagem não enviados só na modalidade HS. Na modalidade HS, os comandos são transmitidos durante o intervalo de vazios vertical.

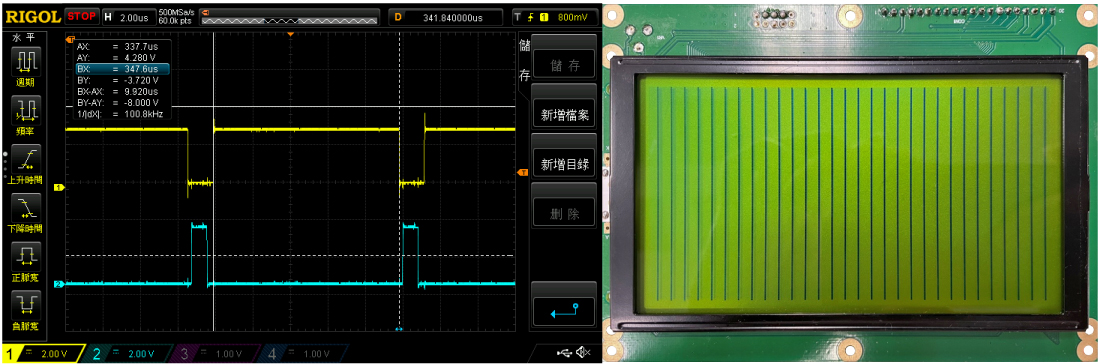

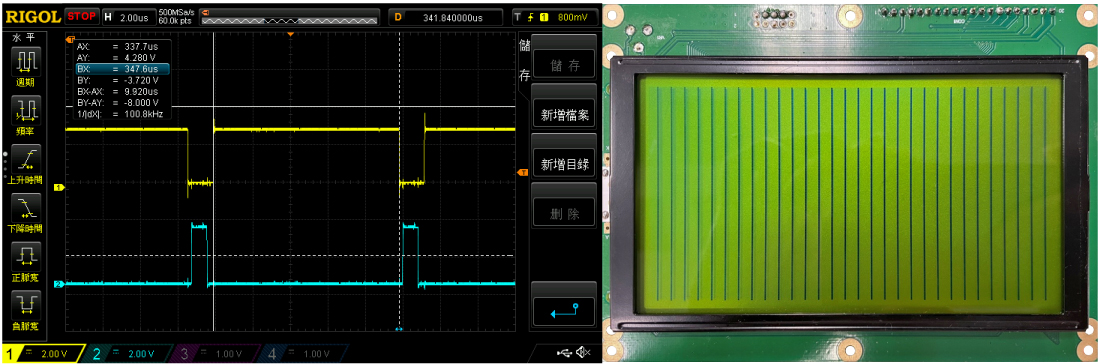

Um exemplo experimental de interface de display MCU 8080/6800:

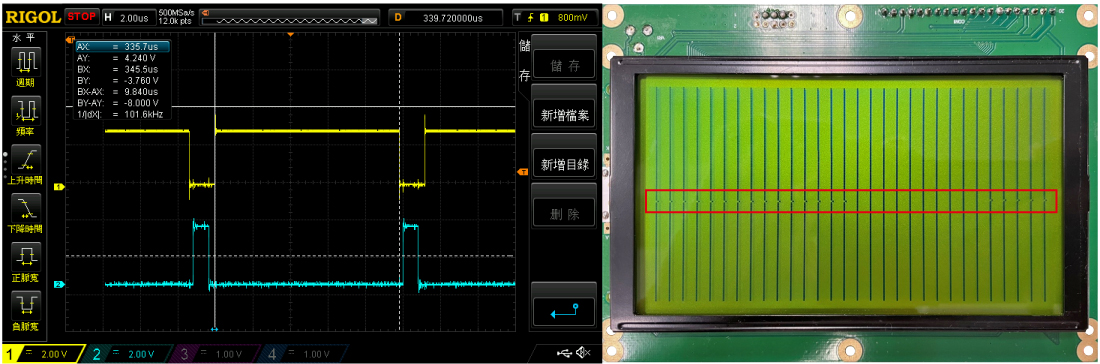

Um controlador LCD foi gradualmente eliminado e o cliente gostaria de ter um módulo compatível pin a pin para substituí-lo. Os proprietários RD tinham projetado um PCB com um MCU para a interface compatível. Os resultados experimentais no sinal HABILITAR devem ter a dimensão mínima de 9,92uS. Isto significa que o máximo BW de comunicação é de aproximadamente 100KBPS.

[Chanel1 –E pin@9.92uS, Chanel2 – CS pin]

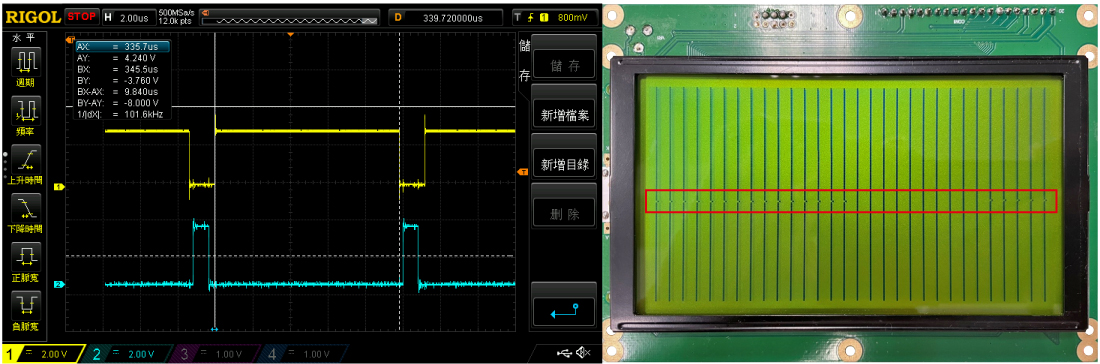

Podemos ver alguns pontos defeituosos quando é diminuído o tempo HABILITAR a 9,84uS (a velocidade de comunicação é até 101KBPS).

[Chanel1 –E pin@9.84uS, Chanel2 – CS pin]

Uma tabela de comparação na interface de display:

Qual interface é a melhor? Não existe uma resposta absoluta a esta pergunta. Os usuários deve escolher a interface adequada para as suas aplicações, não a melhor. Vamos ver a seguinte comparação dos prós e contras destas interfaces.

| Interface de Display |

Resolução |

Velocidade |

Contag. Pin |

Ruídos |

Consumo de Energia |

Distância de Conexão |

Custo |

| MCU 8080/6800 |

Médio |

Baixo |

Mais |

Médio |

Baixo |

Curto |

Baixo |

| RGB 16/18/24 |

Médio |

Rápido |

Mais |

Pior |

Alto |

Curto |

Baixo |

| SPI |

Pequeno |

Baixo |

Menos |

Médio |

Baixo |

Curto |

Baixo |

| I²C |

Pequeno |

Baixo |

Menos |

Médio |

Baixo |

Curto |

Baixo |

| Serial RGB 6/8 |

Médio |

Rápido |

Menos |

Pior |

Alto |

Curto |

Baixo |

| LVDS |

Grande |

Rápido |

Menos |

Melhor |

Baixo |

Comprido |

Alto |

| MIPI |

Grande |

Mais rápido |

Menos |

Melhor |

Baixo |

Curto |

Média |