Préface:

Winstar produit des milliers de modèles de modules d'affichage, y compris TN/STN LCD, OLED, et TFT. Et il y a un grand nombre de types d'interfaces pour transmettre les données d'image au module d'affichage. Les clients peuvent se demander lequel est le meilleur ou peut mieux répondre à leurs besoins. Cet article discute une question concernant le transfert de données des interfaces d'affichage.

La largeur de bande de communication (BW) est un problème important des interfaces d'affichage. Pourquoi le BW est-il important ? Le BW représente la mesure du transfert de données dans le canal de communication. Le BW affecte donc la réponse de l'écran aux données, c'est-à-dire la fréquence de rafraîchissement de l'écran. En d'autres termes, les performances de l'écran.

Introduction:

Les interfaces d'affichage les plus connues aujourd'hui:

1.Parallèle

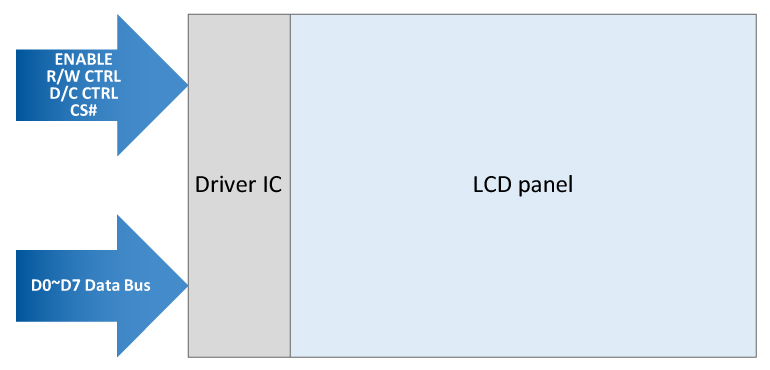

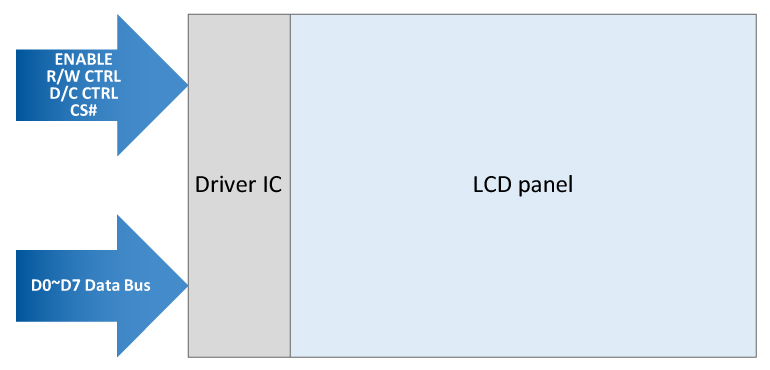

1-1 MCU interface 8080/6800

Les données brutes d'affichage sont envoyées via le bus de données en fonction du signal du bus de commande. La largeur de bande de communication dépend de la vitesse d'activation du circuit intégré du pilote. QVGA 320x240 dot matrix LCD c.-à-d. : la largeur de bande de communication sera 320 * 240 / 8 bit (largeur de données) * 60 fps = 576KHz au signal ACTIVER.

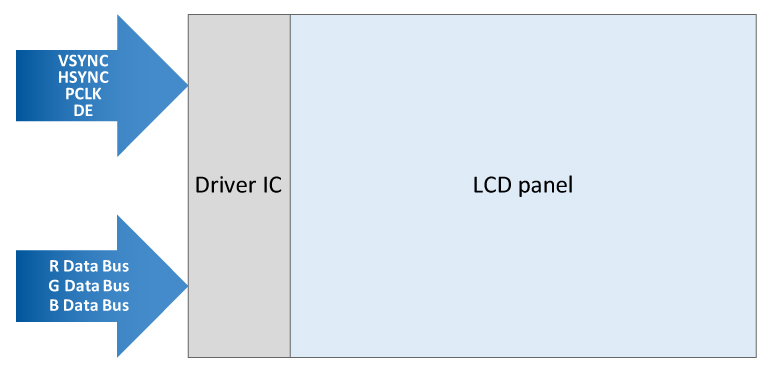

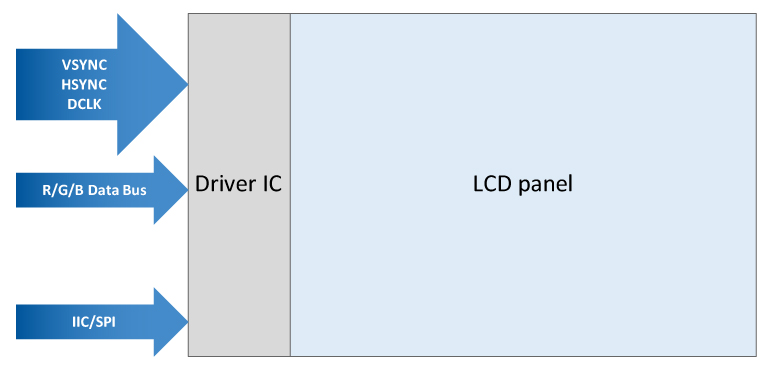

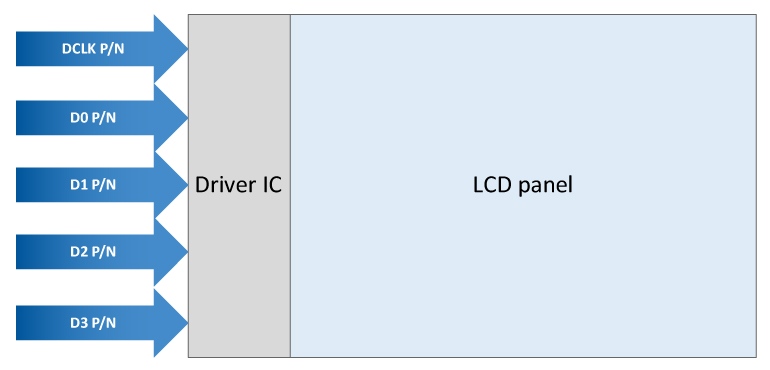

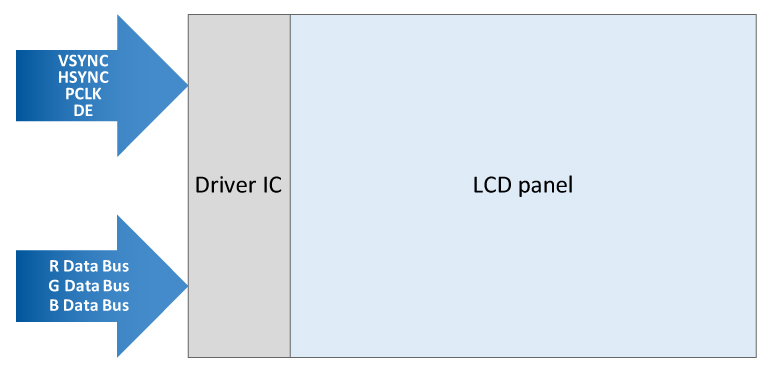

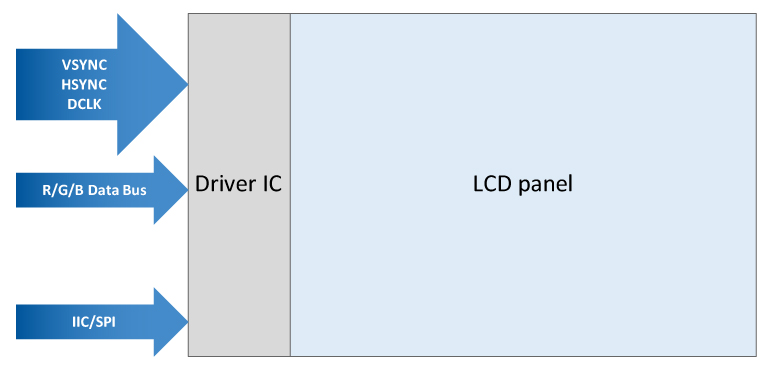

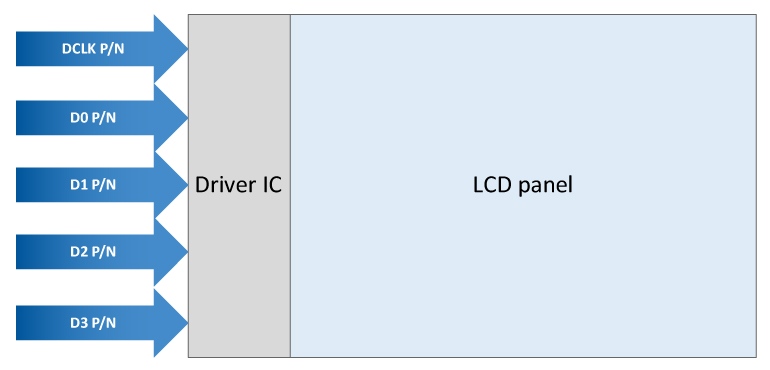

1.2 Parallèle RGB 16/18/24 bits

L'interface RGB permet de transmettre la synchronisation de l'entraînement au circuit intégré de commande de l'écran via l'entrée/sortie des données en parallèle, y compris les données R/G/B, le signal de synchronisation verticale (V-SYNC, signal de synchronisation verticale), le signal de synchronisation horizontale (H-SYNC, signal de synchronisation horizontale), le signal d'activation des données (DE, Activation des données) et le signal d'horloge PCLK (Horloge de pixel). L'interface d'affichage du RGB666 est comme suit:

Les données brutes d'affichage sont transférées de la même manière que ci-dessus. Mais la résolution de l'écran est de plus en plus élevée. Par exemple, WVGA 800 * 480 (pixels) * 60 ips = 23,04 MHz. (PCLK)

2.Série

2.1 SPI (Serial Peripheral Interface - Interface périphérique série)

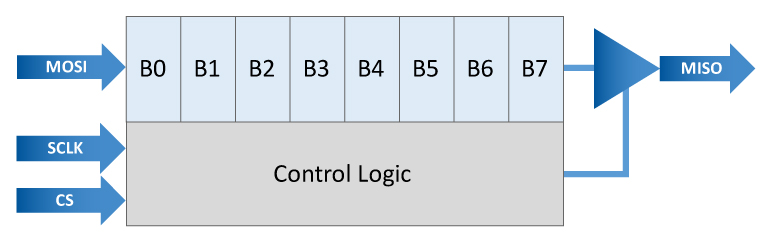

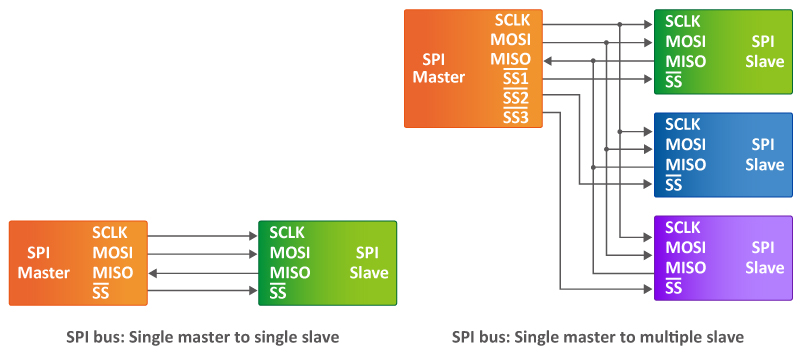

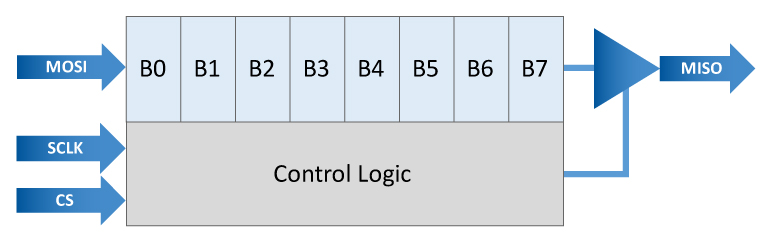

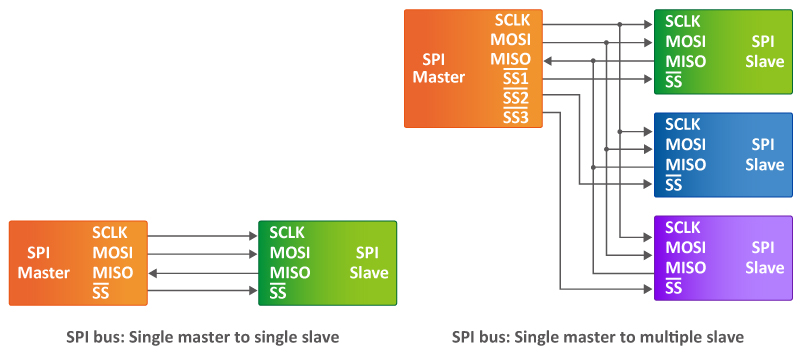

SPI est une interface maître-esclave, généralement avec un maître (dispositif maître) et un ou plusieurs esclaves (dispositifs esclaves). L'interface contient 4 broches. La méthode de connexion et la structure matérielle sont décrites ci-dessous:

[Structure de l'interface SPI]

SCLK: L'horloge synchrone utilisée par tous les appareils. Le maître contrôle cette horloge et les esclaves reçoivent cette horloge.

MOSI: Sortie maître, entrée esclave. C'est la ligne de données principale contrôlée par le maître vers tous les esclaves sur le bus SPI. Seul l'esclave sélectionné reçoit des données de MOSI.

MISO: Entrée maître, sortie esclave. C'est la ligne de données principale contrôlée par l'esclave sélectionné vers le maître. Seul l'esclave sélectionné peut contrôler ce circuit. En fait, c'est le seul circuit de la configuration du bus SPI qu'un esclave est autorisé à contrôler.

CS: Sélection de la puce. Ce signal est unique à chaque esclave. Lorsqu'il est actif, l'esclave sélectionné doit contrôler MISO.

[Exemple de schéma SPI]

Les données d'affichage sont transférées de manière séquentielle. Largeur de bande de communication de l'interface d'affichage, c'est-à-dire QVGA 320 * 240 (pixels) * 16 bits (profondeur de couleur) * 30 ips = 36,864 MHz.

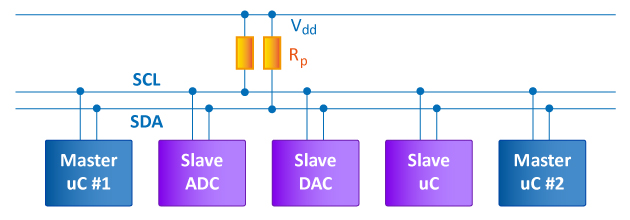

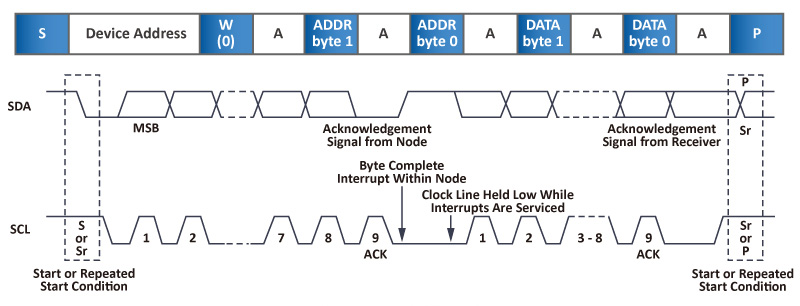

2.2 IIC (Inter-Integrated Circuit - Circuit inter-intégré) ou alternativement connu comme I²C):

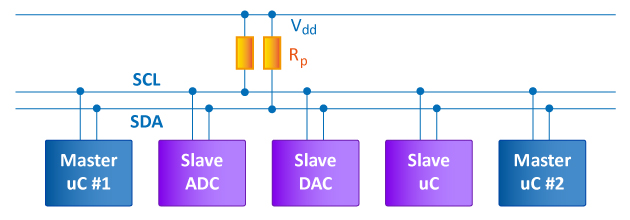

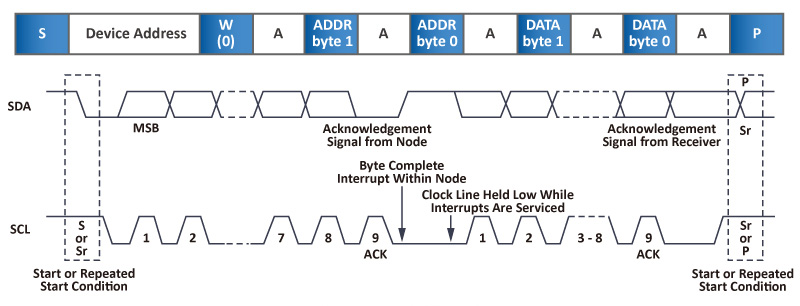

Différente de la base point à point (ou point à multipoint) de SPI, l'interface I²C se présente sous la forme d'un bus de données, qui permet de connecter en série plusieurs dispositifs maîtres et plusieurs dispositifs esclaves. La méthode d’interface et la structure matérielle sont décrites ci-dessous:

[I²C schematic]

[Avec la permission de Analog device]

Standard mode = 100K bit/s.

Full speed mode = 400K bit/s.

Fast mode = 1M bit/s.

High speed mode = 3.2M bit/s.

2.3 Série RGB 6/8 bits.

Les données d'affichage sont transférées de manière séquentielle RGB. Largeur de bande de communication de l'interface d'affichage, c'est-à-dire QVGA 320 * 240 (pixels) * 3 points * 30 ips = 6912000 Hz (DCLK).

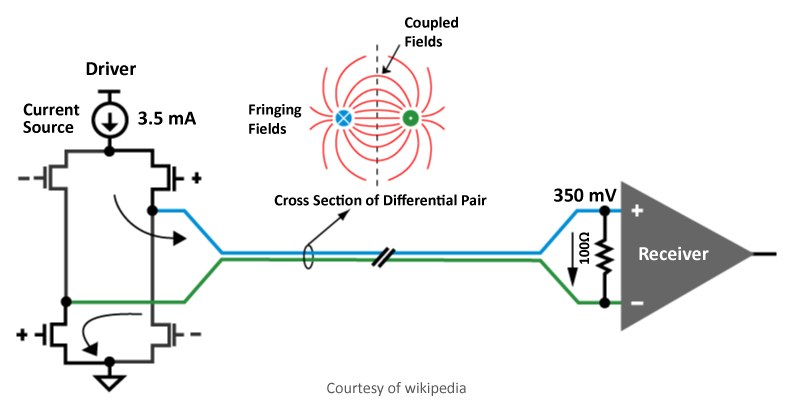

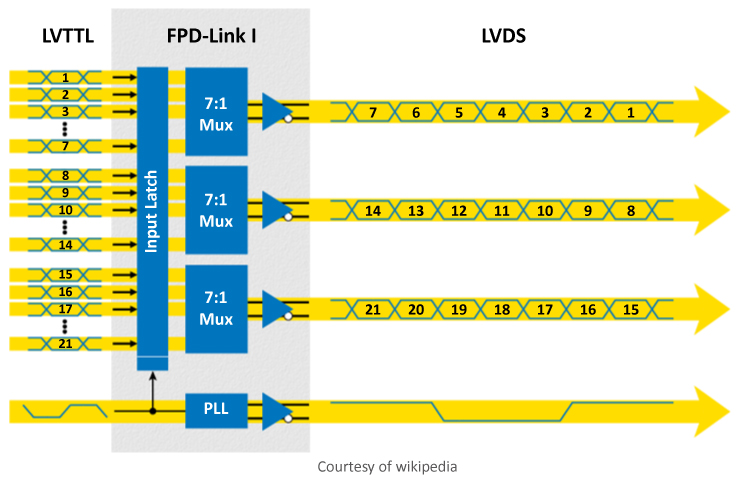

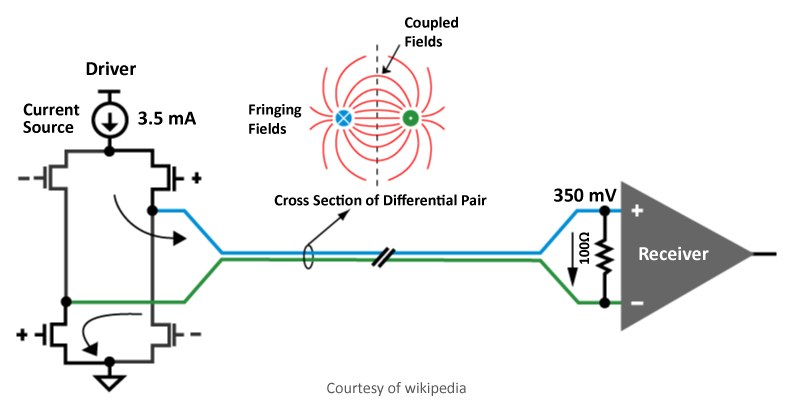

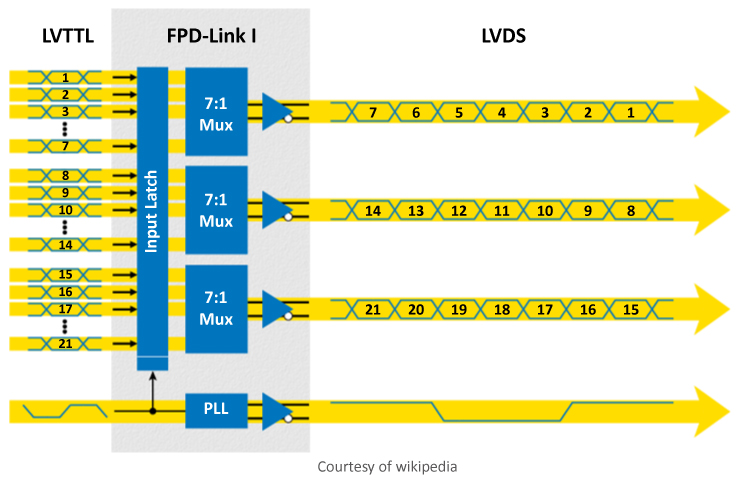

2.4 LVDS: Signal différentiel à basse tension. Il devrait être nommé FPD-Link pour l'interface d'affichage.

LVDS est une norme technique introduite en 1994 qui spécifie les caractéristiques électriques d'une norme de signalisation différentielle et série, mais ce n'est pas un protocole. LVDS est une spécification de la couche physique uniquement ; de nombreuses normes et applications de communication de données l'utilisent et y ajoutent une couche de liaison de données telle que définie dans le modèle OSI. LVDS fonctionne à faible puissance et peut fonctionner à des vitesses très élevées en utilisant des câbles en cuivre à paire torsadée économiques.

Au début, les vendeurs d'ordinateurs portables et d'écrans LCD utilisaient souvent le terme LVDS au lieu de FPD-Link pour désigner leur protocole. Le terme LVDS est devenu, par erreur, synonyme de Lien d’affichage à plat dans le vocabulaire de l'ingénierie des écrans vidéo.

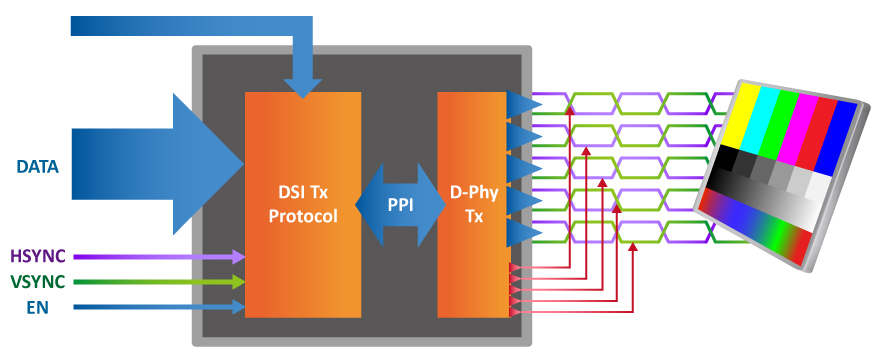

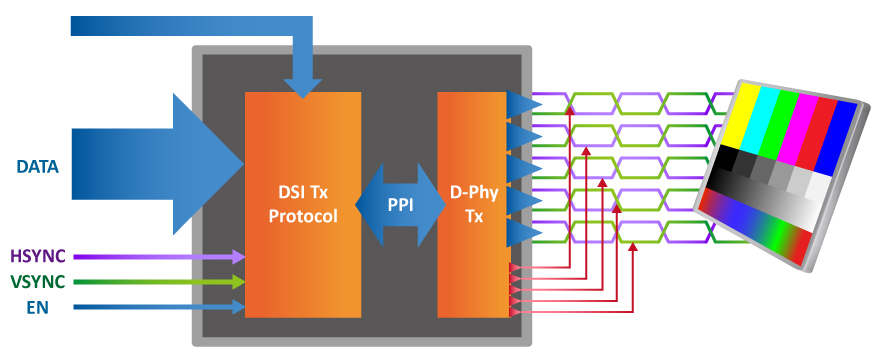

2.5 MIPI CSI/DSI : Mobile Industry Processor Interface.

[Affichage DSI]

MIPI Alliance vise à réduire le coût des contrôleurs d'affichage dans les appareils mobiles. Elle définit un bus série et un protocole de communication entre l'hôte, la source des données d'image, et le dispositif de destination. Elle est la norme attendue des technologies d'affichage LCD et similaires.

[Vue du système de la DSI]

DSI spécifie un bus série point à point de signalisation différentielle à haut débit (par exemple, 4,5 Gbit/s/voie pour D-PHY 2.0). Ce bus contient une voie d'horloge à haut débit et une ou plusieurs voies de données.

Les données d'image sur le bus sont entrelacées avec des signaux d'intervalles de suppression horizontale et verticale. Les données sont transférées à l'écran en temps réel et ne sont pas stockées sur le dispositif pour économiser la mémoire tampon de l'image dans l'écran. Cependant, cela signifie également que l'appareil doit être rafraîchi en permanence (à une fréquence de 30 ou 60 images par seconde) sous risque de perdre l'image. Les données d'image ne sont envoyées qu'en mode HS. En mode HS, les commandes sont transmises pendant l'intervalle de suppression verticale.

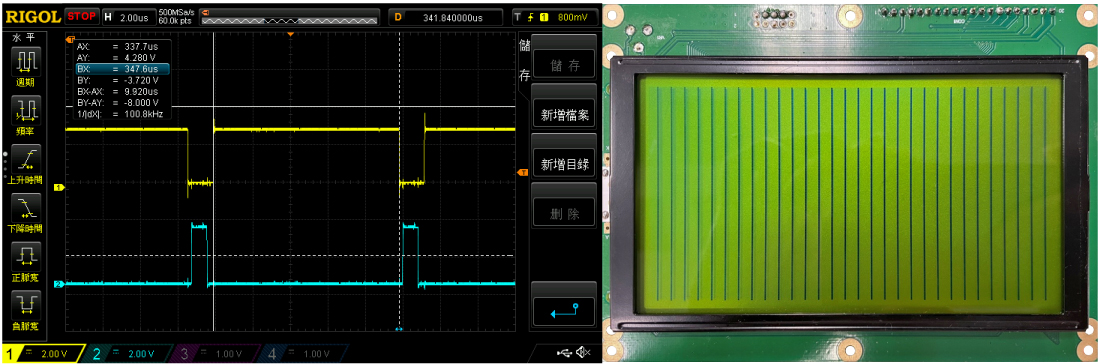

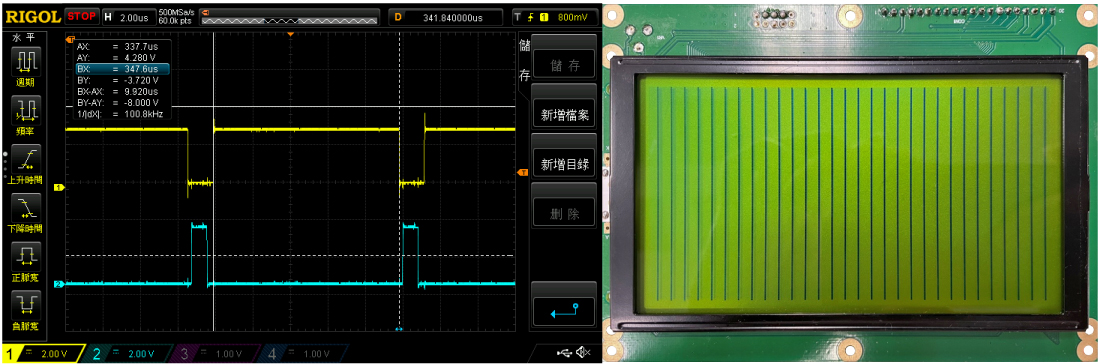

Un exemple expérimental d'interface d'affichage MCU 8080/6800:

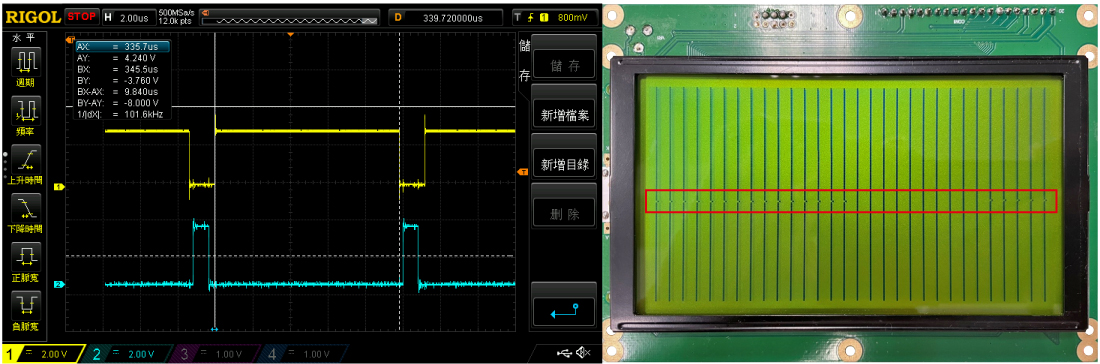

Un contrôleur LCD n’est plus produit et le client souhaiterait disposer d'un module compatible broche à broche pour le remplacer. Les propriétaires de RD ont conçu un PCB avec un MCU pour l'interface compatible. Les résultats expérimentaux sur le signal ACTIVER doivent être aussi longs que 9,92uS au moins. Cela signifie que le BW maximal de communication est d'environ 100KBPS.

[Chanel1 –E pin@9.92uS, Chanel2 – CS pin]

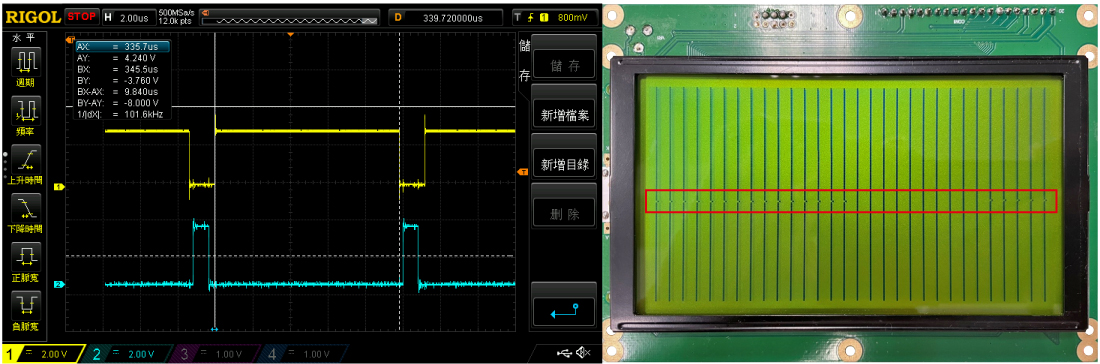

Nous pouvons voir quelques points défectueux ci-dessous en raccourcissant le temps de ACTIVER à 9,84uS (la vitesse de communication est jusqu'à 101KBPS).

[Chanel1 –E pin@9.84uS, Chanel2 – CS pin]

Tableau comparatif des interfaces d'affichage:

Quelle interface est la meilleure ? Il n'y a pas de réponse définitive à cette question. Les utilisateurs doivent choisir l'interface qui convient à leurs applications, et non la meilleure. Voici un tableau comparatif des avantages et des désavantages de ces interfaces.

| Interface d'affichage |

Résolution |

Vitesse |

Nombre de broches |

Bruit |

Consommation électrique |

Distance de connexion |

Coût |

| MCU 8080/6800 |

Moyen |

Faible |

Élevé |

Moyen |

Faible |

Court |

Faible |

| RGB 16/18/24 |

Moyen |

Rapide |

Élevé |

Pire |

Élevé |

Court |

Faible |

| SPI |

Petit |

Faible |

Moins |

Moyen |

Faible |

Court |

Faible |

| I²C |

Petit |

Faible |

Moins |

Moyen |

Faible |

Court |

Faible |

| Serial RGB 6/8 |

Middle |

Rapide |

Moins |

Pire |

Élevé |

Court |

Faible |

| LVDS |

Large |

Rapide |

Moins |

Meilleur |

Faible |

Long |

Élevé |

| MIPI |

Large |

Très rapide |

Moins |

Meilleur |

Faible |

Court |

Moyen |