我們重視您的隱私

通過點擊「允許所有 Cookie」,代表您同意在您的設備上存儲 Cookie 以增強網站瀏覽體驗、分析網站使用情況並協助我們的行銷和網站效能優化工作。您可以在我們的隱私權政策中找到有關於此的更多資訊。

WF70A8TYAHMNN0 是一款 7吋 MIPI DSI介面 1024 x 600 IPS TFT-LCD 模組。此TFT-LCD採用IPS技術,具左:85 /右:85 /上:85 /下:85度的廣視角,對比度800:1(典型值),亮度600 nits (典型值),使用防眩光面板,長寬比 16:9。如果客戶需要高亮度,可以考慮選擇我們 WF70A8SYAHMNN0 (1100 cd/m²)。

WF70A8系列提供投射電容式觸控面板(PCAP)和電阻式觸控面板(RTP)選項,也可用於LVDS 介面,可靈活滿足不同的系統整合需求。如需了解有關具體型號的更多訊息,請隨時透過我們的網站與我們聯繫。

WF70A8TYAHMNN0 TFT模組內建EK7900AD3和EK73217BCGA驅動IC;支援 4線 MIPI 介面 (Mobile Industry Processor Interface) DSI (Display Serial Interface),由於MIPI介面具有高速率Data傳輸和高速率Clock傳輸的特性, 使得 MIPI介面越來越受市場歡迎。WF70A8TYAHMNN0 模組具有防眩光面板;長寬比16:9,工作溫度範圍-20℃~+70℃;儲存溫度範圍為-30℃~+80℃。

| 項目 | 規格 | 單位 |

|---|---|---|

| 顯示尺寸(對角線) | 7.0 | 吋 |

| 點陣(解析度) | 1024 x RGB x 600(TFT) | dots |

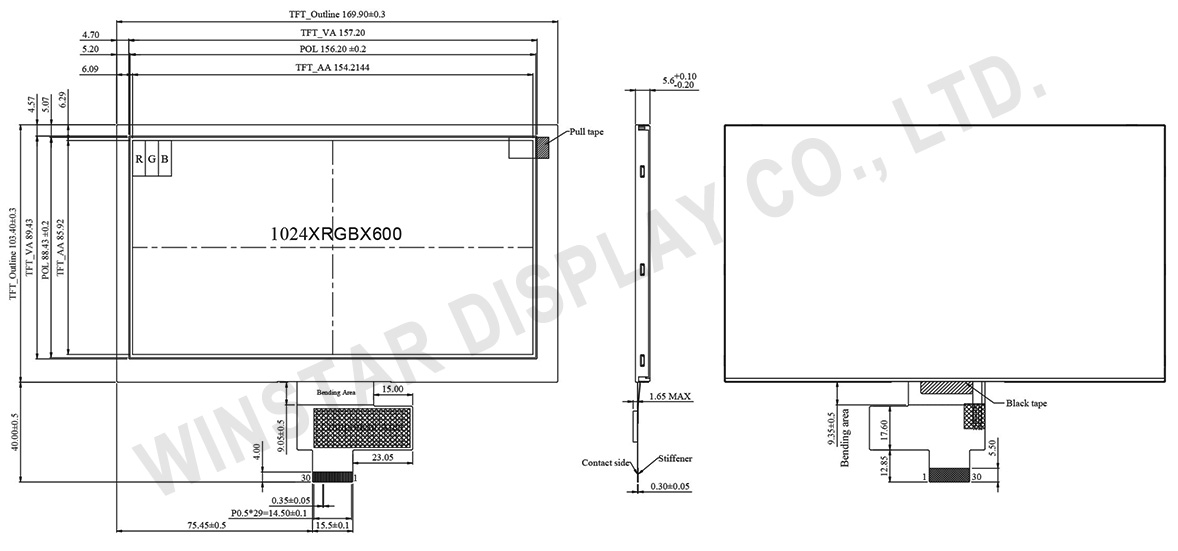

| 模組尺寸 | 169.9(W) × 103.4(H) × 5.6(D) | mm |

| 有效區域 | 154.2114 x 85.92 | mm |

| 點間距 | 0.1506 x 0.1432 | mm |

| LCD類型 | TFT, 正常白, 透射性 | |

| 視角 | 85/85/85/85 | |

| 長寬比 | 16:9 | |

| 驅動 IC | EK79007AD3 + EK73217BCGA或相容IC | |

| 介面 | 4-Lanes MIPI | |

| 背光類型 | LED, 正常白 | |

| 觸控面板類型 | 無 | |

| 表面 | 防眩光 | |

| 項目 | 符號 | 最小值 | 典型值 | 最大值 | 單位 |

|---|---|---|---|---|---|

| 工作溫度 | TOP | -20 | - | +70 | ℃ |

| 儲存溫度 | TST | -30 | - | +80 | ℃ |

| 項目 | 符號 | 標準值 | 單位 | ||

|---|---|---|---|---|---|

| 最小值 | 典型值 | 最大值 | |||

| 電壓 | VDD | 1.71 | 1.8 | 1.89 | V |

| 類比電壓 | AVDD | 8.9 | 9.0 | 9.1 | V |

| TFT VGH 電壓 | VGH | 17 | 18 | 19 | V |

| TFT VGL 電壓 | VGL | -6.5 | -6.0 | -5.5 | V |

| TFT VCOMIN 電壓 | VCOMIN | 3.0 | 3.15 | 3.3 | V |

| 驅動電流 | IDD | -- | 16 | 24 | mA |

| 電源電流 | IAVDD | -- | 19 | 28.5 | mA |

| TFT IVGH 電流 | IVGH | -- | 1.6 | 2.4 | mA |

| TFT IVGL 電流 | IVGL | -- | 0.6 | 0.9 | mA |

| TFT IVCOMIN 電流 | IVCOMIN | -- | 0 | -- | mA |

| 項目 | 符號 | 標準值 | 單位 | ||

|---|---|---|---|---|---|

| 最小值 | 典型值 | 最大值 | |||

| LED 背光電壓 | VL | 16.8 | 19.2 | 21.0 | V |

| LED 背光電流 | IL | -- | 240 | -- | mA |

| LED 使用壽命 | - | - | 50,000 | - | Hr |

| Pin No. | 符號 | 功能說明 |

|---|---|---|

| 1 | VLED+ | LED Anode |

| 2 | VLED+ | LED Anode |

| 3 | VGH | Positive power for TFT |

| 4 | VGL | Negative power for TFT |

| 5 | UPDN | Gate up or down scan control. UPDN = ”L”, STV2 output vertical start pulse and UD pin output logical “L” to Gate driver. (default) UPDN = ”H”, STV1 output vertical start pulse and UD pin output logical “H” to Gate driver |

| 6 | SHLR | Source right or left sequence control. SHLR = ”L“, shift left: last data = S1←S2←S3….......←S1536 = first data. SHLR = ”H“, shift right: first data = S1→S2→S3….....→S1536 = last data.(default) |

| 7 | VLED- | LED Cathode |

| 8 | VLED- | LED Cathode |

| 9 | AVDD | Power for Analog Circuit |

| 10 | GND | Ground |

| 11 | D3P | MIPI data input. |

| 12 | D3N | MIPI data input. |

| 13 | GND | Ground |

| 14 | D2P | MIPI data input. |

| 15 | D2N | MIPI data input. |

| 16 | GND | Ground |

| 17 | CLKP | MIPI clock input |

| 18 | CLKN | MIPI clock input |

| 19 | GND | Ground |

| 20 | D1P | MIPI data input. |

| 21 | D1N | MIPI data input. |

| 22 | GND | Ground |

| 23 | D0P | MIPI data input. |

| 24 | D0N | MIPI data input. |

| 25 | GND | Ground |

| 26 | STBYB | Standby mode. STBYB = ”H“,normal operation(default) STBYB = ”L”, timing controller, source driver will turn off, all output are GND. |

| 27 | RESET | Global reset pin. Active Low to enter Reset State. Normally pull high. Connecting with an RC reset circuit for stability. |

| 28 | VDD(1.8V) | Digital circuit |

| 29 | VDD(1.8V) | Digital circuit |

| 30 | VCOMIN | Common voltage |

通過點擊「允許所有 Cookie」,代表您同意在您的設備上存儲 Cookie 以增強網站瀏覽體驗、分析網站使用情況並協助我們的行銷和網站效能優化工作。您可以在我們的隱私權政策中找到有關於此的更多資訊。