私たちはあなたのプライバシーを大切にします

「すべてのクッキーを許可」をクリックすると、サイトのナビゲーションを向上させ、サイト使用状況を分析し、マーケティングおよびパフォーマンスの取り組みを支援するために、クッキーをデバイスに保存することに同意したことになります。この件に関する詳細情報は、ポリシーをご覧ください。プライバシーポリシー

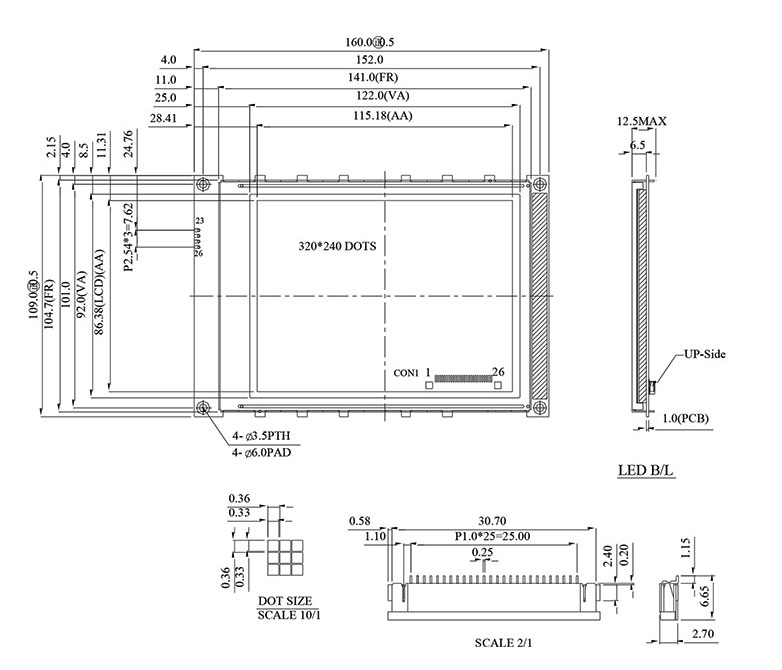

WG320240BP3 は、S1D13700 コントローラーを使用した 5.67 インチのグラフィック LCD モジュールです。26ピン ZIF コネクターと内蔵のアナログタッチパネルドライバーを搭載しています。6800/8080 インターフェース、内蔵の負電圧発生器、オプションの温度補償に対応しています。このモデルは、タッチ機能内蔵を必要とするアプリケーションに適しています。

他のモデルとの比較:

| 項目 | 標準値 | 単位 |

|---|---|---|

| ドットマトリクス(解像度) | 320x240 | - |

| モジュールサイズ | 160.0 x 109.0 x 12.5(MAX) | mm |

| 表示エリア | 122.0 x 92.0 | mm |

| 有効エリア | 115.18 x 86.38 | mm |

| ドットサイズ | 0.33 x 0.33 | mm |

| ドットピッチ | 0.36 x 0.36 | mm |

| Duty | 1/240 | |

| バックライトタイプ | LED | |

| IC | S1D13700 | |

| 項目 | 記号 | 最小値 | 典型値 | 最大値 | 単位 |

|---|---|---|---|---|---|

| 動作温度 | TOP | -20 | - | 70 | ℃ |

| 保存温度 | TST | -30 | - | 80 | ℃ |

| 入力電圧 | VIN | -0.3 | - | VDD+0.5 | V |

| 出力電圧 | VOUT | -0.3 | - | VDD+0.5 | V |

| ロジック電源電圧 | VDD-VSS | 0 | - | 6.5 | V |

| LCD電源電圧 | VDD-V0 | 0 | - | 32 | V |

| 項目 | 記号 | 条件 | 最小値 | 典型値 | 最大値 | 単位 |

|---|---|---|---|---|---|---|

| ロジック電源電圧 | VDD-VSS | - | 4.5 | 5.0 | 5.5 | V |

| LCD電源電圧 | VDD-V0 | Ta=-20℃ Ta=25℃ Ta=70℃ |

- 23.0 22.2 |

- 23.6 - |

26.1 24.2 - |

V V V |

| 入力電圧(High) | VIH | - | 3.5 | - | - | V |

| 入力電圧(Low) | VIL | - | - | - | 1.0 | V |

| 出力電圧(High) | VOH | - | VDD-0.4 | - | - | V |

| 出力電圧(Low) | VOL | - | - | - | 0.4 | V |

| 供給電流 | IDD | VDD=5.0V | 65.0 | 75.0 | 85.0 | mA |

| Pin No. | 記号 | Level | 説明 |

|---|---|---|---|

| 1 | VSS | 0V | Ground |

| 2 | VDD | 5.0V | Power supply for Logic |

| 3 | VO | (Variable) | Driving voltage for LCD |

| 4 | A0 | H/L | RD=L WR=H ,A0=L :Data Read AO=H :Status read RD=H WR=L ,A0=L :Data Write AO=H :Command write |

| 5 | ___ WR |

H/L | 8080 family: Write signal, 6800 family: R/W signal |

| 6 | ___ RD |

H/L | 8080 family: Read signal, 6800 family: Enable clock |

| 7~14 | DB0~DB7 | H/L | Data bus line |

| 15 | ___ CS |

H/L | Chip select ,Active L |

| 16 | ___ RES |

H/L | Controller reset signal, Active L |

| 17 | Vee | Negative Voltage Output | |

| 18 | SEL1 | 8080 or 6800 interface select | |

| 19 | DCLK | External Clock Input. This clock runs the SAR conversion process and synchronizes serial data I/O. | |

| 20 | /CS | Chip Select Input. Controls conversion timing and enables the serial input/output register. CS high = power-down mode (ADC only). | |

| 21 | DIN | Serial Data Input. If CS is low, data is latched on rising edge of DCLK. | |

| 22 | DOUT | Serial Data Output. Data is shifted on the falling edge of DCLK. This output is high impedance when CS is high. | |

| 23 | PEN | Pen Interrupt. Open anode output (requires 10kΩ to 100kΩ pull-up resistor externally). | |

| 24 | PEN1 | Pen Interrupt. Open anode output (requires 10kΩ to 100kΩ pull-up resistor externally). | |

| 25 | NC | No connection | |

| 26 | AUX | Auxiliary Input to AD |

Search Keyword: 320x240 lcd, 320 x 240 lcd, lcd 320 x240

「すべてのクッキーを許可」をクリックすると、サイトのナビゲーションを向上させ、サイト使用状況を分析し、マーケティングおよびパフォーマンスの取り組みを支援するために、クッキーをデバイスに保存することに同意したことになります。この件に関する詳細情報は、ポリシーをご覧ください。プライバシーポリシー