私たちはあなたのプライバシーを大切にします

「すべてのクッキーを許可」をクリックすると、サイトのナビゲーションを向上させ、サイト使用状況を分析し、マーケティングおよびパフォーマンスの取り組みを支援するために、クッキーをデバイスに保存することに同意したことになります。この件に関する詳細情報は、ポリシーをご覧ください。プライバシーポリシー

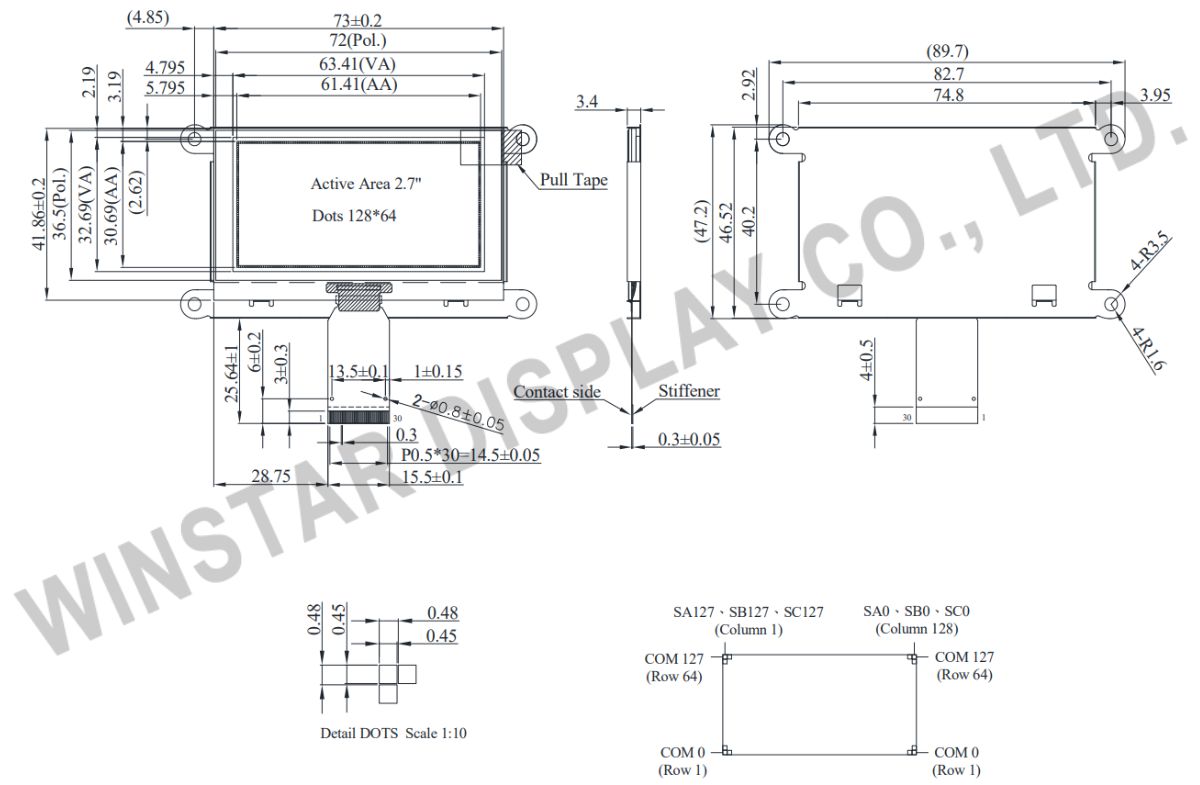

| 項目 | 仕様 | Unit |

|---|---|---|

| ドットマトリックス(解像度) | 128 × 64 | dots |

| モジュールサイズ | 89.72 × 47.2 ×3.4 | mm |

| 有効エリア | 61.4 × 30.69 | mm |

| ピクセルサイズ | 0.45 × 0.45 | mm |

| ピクセルピッチ | 0.48 × 0.48 | mm |

| 表示モード | パッシブマトリクス | |

| 発光色 | 有機EL白色 | |

| 駆動方法 | 1/64 Duty | |

| グレースケール | 4 bits | |

| IC | SSD1357 | |

| インターフェイス | 8-bits 6800 and 8080 parallel, 4-line SPI, I2C | |

| サイズ (対角線) | 2.7 インチ | |

| パラメーター | 記号 | 最小値 | 最大値 | 単位 |

|---|---|---|---|---|

| ロジック電源電圧 | VDD | -0.3 | 4 | V |

| Display電源電圧 | VCC | 0 | 15 | V |

| 操作温度 | TOP | -40 | +80 | °C |

| 保存温度 | TSTG | -40 | +85 | °C |

| 項目 | 記号 | 条件 | 最小値 | 典型値 | 最大値 | 単位 |

|---|---|---|---|---|---|---|

| ロジック電源電圧 | VDD | - | 1.65 | 3.0 | 3.3 | V |

| Display電源電圧 | VCC | - | 8.0 | 9.0 | 9.5 | V |

| 高レベル入力 | VIH | - | 0.8×VDD | - | VDD | V |

| 低レベル入力 | VIL | - | 0 | - | 0.2×VDD | V |

| 高レベル出力 | VOH | - | 0.9×VDD | - | VDD | V |

| 低レベル出力 | VOL | - | 0 | - | 0.1×VDD | V |

| Display 50% Pixel on | ICC | VCC =9V | - | 31.5 | 47.5 | mA |

| Pin No. | 記号 | 功能説明 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | NC(GND) | No connection | |||||||||||||||

| 2 | VSS | Ground of Logic Circuit. This is a ground pin. It also acts as a reference for the logic pins. It must be connected to external ground. |

|||||||||||||||

| 3 | VCC | Power supply for panel driving voltage. This is also the most positive power voltage supply pin. | |||||||||||||||

| 4 | VCOMH | Voltage Output High Level for COM Signal. This pin is the input pin for the voltage output high level for COM signals. A tantalum capacitor should be connected between this pin and VSS. |

|||||||||||||||

| 5 | VLSS | Ground of Analog Circuit These are the analog ground pins. They should be connected to VSS externally. |

|||||||||||||||

| 6~13 | D7~D0 | These pins are bi-directional data bus connecting to the MCU data bus.Unused pins are recommended to tie LOW. When serial interface mode is selected, D0 will be the serial clock input: SCLK; D1 will be the serial data input: SDIN and D2 should be kept NC. When I2C mode is selected, D2, D1 should be tied together and serve as SDAout,SDAin in application and D0 is the serial clock input, SCL. |

|||||||||||||||

| 14 | E/RD# | This pin is MCU interface input. When 6800 interface mode is selected, this pin will be used as the Enable (E) signal. Read/write operation is initiated when this pin is pulled HIGH and the chip is selected. When 8080 interface mode is selected, this pin receives the Read (RD#) signal. Read operation is initiated when this pin is pulled LOW and the chip is selected. When serial or I2C interface is selected, this pin must be connected to VSS. |

|||||||||||||||

| 15 | R/W# | This pin is read / write control input pin connecting to the MCU interface. When 6800 interface mode is selected, this pin will be used as Read/Write (R/W#) selection input. Read mode will be carried out when this pin is pulled HIGH and write mode when LOW. When 8080 interface mode is selected, this pin will be the Write (WR#) input. Data write operation is initiated when this pin is pulled LOW and the chip is selected. When serial or I2C interface is selected, this pin must be connected to VSS. |

|||||||||||||||

| 16 17 |

BS1 BS2 |

Communicating Protocol Select. These pins are MCU interface selection input. See the following table:

|

|||||||||||||||

| 18 | D/C# | This pin is Data/Command control pin connecting to the MCU. When the pin is pulled HIGH, the data at D[7:0] will be interpreted as data. When the pin is pulled LOW, the data at D[7:0] will be transferred to a command register. In I2C mode, this pin acts as SA0 for slave address selection.When 3-wire serial interface is selected, this pin must be connected to VSS. |

|||||||||||||||

| 19 | CS# | Chip SelectThis pin is the chip select input. The chip is enabled for MCU communication onlywhen CS# is pulled low. |

|||||||||||||||

| 20 | RES# | This pin is reset signal input. When the pin is pulled LOW, initialization of the chip is executed.Keep this pin pull HIGH during normal operation. |

|||||||||||||||

| 21 | FR | Frame Frequency Triggering Signal This pin will send out a signal that could be used to identify the driver status. Nothing should be connected to this pin. It should be left open individually. |

|||||||||||||||

| 22 | IREF | This pin is the segment output current reference pin. IREF is supplied externally. |

|||||||||||||||

| 23 | N.C | Reserved Pin The N.C. pin between function pins is reserved for compatible and flexible design. |

|||||||||||||||

| 24 | VDD | Power Supply for I/O Pin. This pin is a power supply pin of I/O buffer. It should be connected to VCI or external source. All I/O signal should have VIH reference to VDDIO. When I/O signal pins (BS0~BS1, D0~D7, control signals…) pull high, they should be connected to VDDIO. |

|||||||||||||||

| 25 | VP | Power Supply for Core Logic Circuit This is a voltage supply pin. It can be supplied externally (within the range of 2.4~2.6V) or regulated internally from VCI. A capacitor should be connected between this pin & VSS under all circumstances. |

|||||||||||||||

| 26 | VDD | Power Supply for Operation. This is a voltage supply pin. It must be connected to external source & always be equal to or higher than VDD & VDDIO. |

|||||||||||||||

| 27 | VSL | Voltage Output Low Level for SEG Signal This is segment voltage (output low level) reference pin. This pin has to connect with resistor and diode to ground (details depends on application). |

|||||||||||||||

| 28 | VLSS | Ground of Analog Circuit These are the analog ground pins. They should be connected to VSS externally. |

|||||||||||||||

| 29 | VLSS | Power Supply for OEL Panel These are the most positive voltage supply pin of the chip. They must be connected to external source. |

|||||||||||||||

| 30 | NC(GND) | No connection |

「すべてのクッキーを許可」をクリックすると、サイトのナビゲーションを向上させ、サイト使用状況を分析し、マーケティングおよびパフォーマンスの取り組みを支援するために、クッキーをデバイスに保存することに同意したことになります。この件に関する詳細情報は、ポリシーをご覧ください。プライバシーポリシー