我们重视您的隐私

通过点击「允许所有 Cookie」,代表您同意在您的设备上存储 Cookie 以增强网站浏览体验、分析网站使用情况并协助我们的营销和网站效能优化工作。您可以在我们的隐私权政策中找到有关于此的更多信息。

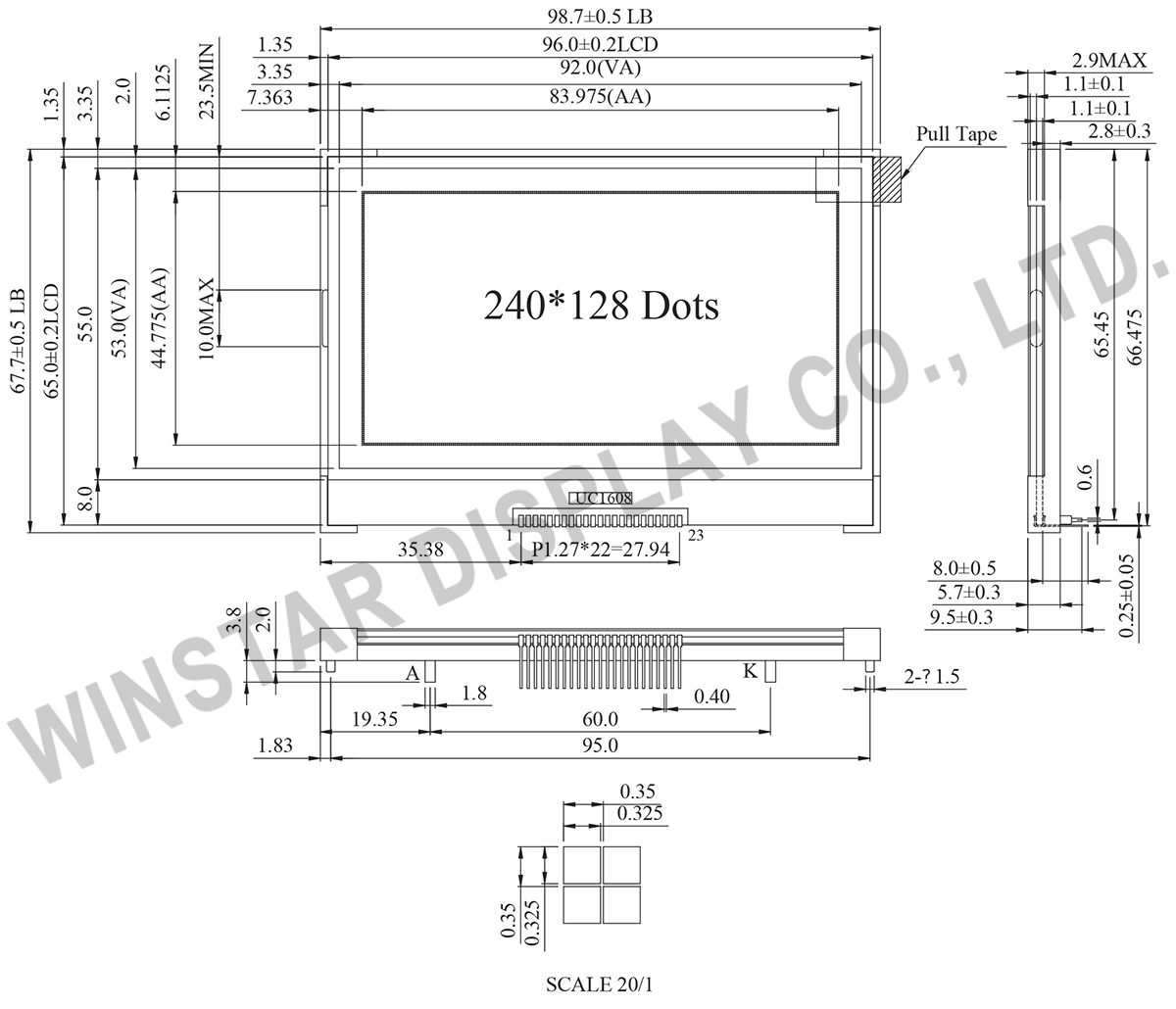

WO240128A 是一款 3.75 英寸单色图形 LCD 模组,采用 COG(Chip on Glass)结构设计,分辨率为 240x128 dots,内建 UC1608 控制 IC,支持多种接口类型(6800、8080、3 线 SPI、4 线 SPI)。该模组具有轻薄、省电等特点,适用于工业仪器、医疗设备及手持式装置等对显示品质和空间效率有较高要求的应用。提供多种 LCD 类型和偏光片模式,欢迎联系我们了解更多信息。

| 项目 | 标准尺寸 | 单位 |

|---|---|---|

| 显示内容 | 240 x 128 点 | - |

| 模块尺寸 | 98.7 x 67.7 x 9.5 (Max) | mm |

| 检视区域 | 92.0 x 53.0 | mm |

| 有效区域 | 83.975 x 44.775 | mm |

| 点大小 | 0.325 x0.325 | mm |

| 点间距 | 0.35 x 0.35 | mm |

| 驱动方式 | 1/128 , 1/12 Bias | |

| 背光类型 | LED | |

| IC | UC1608 | |

| 接口 | 6800/8080/3 wire SPI/4 wire SPI | |

| 项目 | 符号 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| 工作温度 | TOP | -20 | - | +70 | ℃ |

| 储存温度 | TST | -30 | - | +80 | ℃ |

| 逻辑电源电压 | VDD | -0.3 | - | +4.0 | V |

| LCD Generator supply voltage | VDD2 | -0.3 | - | +4.0 | V |

|

LCD Generated voltage |

VLCD | -0.3 | - | +17.8 | V |

| 项目 | 符号 | 条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|---|

| 逻辑电源电压 | VDD-VSS | - | 2.7 | 2.8~3.3 | 3.6 | V |

| LCM电源电压 | V0-VSS | Ta=-20℃ Ta=25℃ Ta=70℃ |

- 15.2 - |

- 15.5 - |

- 15.8 - |

V V V |

| 输入高电压 | VIH | - | 0.8 VDD | - | - | V |

| 输入低电压 | VIL | - | - | - | 0.2VDD | V |

| 输出高电压 | VOH | - | 0.8VDD | - | - | V |

| 输出低电压 | VOL | - | - | - | 0.2VDD | V |

| 供电电流(不包括LED背光) | IDD | VDD=3.0V | - | 1.1 | - | mA |

| Pin No. | 符号 | Level | 说明 | |||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | VB1- | PWR | LCD Bias Voltages. These are the voltage source to provide SEG driving currents. These voltages are generated internally. Connect capacitors of CBX between VBX+ and VBX–. The resistance of these four traces directly affects the SEG driving strength of the resulting LCD module. Minimize the trace resistance is critical in achieving high quality image. |

|||||||||||||||||||||||||||||||||||||||||||||

| 2 | VB1+ | |||||||||||||||||||||||||||||||||||||||||||||||

| 3 | VB0- | |||||||||||||||||||||||||||||||||||||||||||||||

| 4 | VB0+ | |||||||||||||||||||||||||||||||||||||||||||||||

| 5 | VLCD | PWR | Main LCD Power Supply. Connect these pins together. | |||||||||||||||||||||||||||||||||||||||||||||

| 6 | VBIAS | I | This is the reference voltage to generate the actual SEG driving voltage. VBIAS can be used to fine tune VLCD by external variable resistors. Internal resistor network has been provided to simplify external trimming circuit. In COF application, connect a small bypass capacitor between VBIAS and VSS to reduce noise. |

|||||||||||||||||||||||||||||||||||||||||||||

| 7 | VSS | PWR | Ground | |||||||||||||||||||||||||||||||||||||||||||||

| 8 | VDD | PWR | Supply Voltage for logic | |||||||||||||||||||||||||||||||||||||||||||||

| 9 | D7 | I/O | Bi-directional bus for both serial and parallel host interfaces. In serial modes, connect D[0] to SCK, D[3] to SDA,

|

|||||||||||||||||||||||||||||||||||||||||||||

| 10 | D6 | |||||||||||||||||||||||||||||||||||||||||||||||

| 11 | D5 | |||||||||||||||||||||||||||||||||||||||||||||||

| 12 | D4 | |||||||||||||||||||||||||||||||||||||||||||||||

| 13 | D3 | |||||||||||||||||||||||||||||||||||||||||||||||

| 14 | D2 | |||||||||||||||||||||||||||||||||||||||||||||||

| 15 | D1 | |||||||||||||||||||||||||||||||||||||||||||||||

| 16 | D0 | |||||||||||||||||||||||||||||||||||||||||||||||

| 17 | WR1 | I | WR[1:0] controls the read/write operation of the host interface. See Host Interface section for more detail. In parallel mode, WR[1:0] meaning depends on whether the interface is in the 6800 mode or the 8080 mode. In serial interface modes, these two pins are not used, connect them to VSS. |

|||||||||||||||||||||||||||||||||||||||||||||

| 18 | WR0 | |||||||||||||||||||||||||||||||||||||||||||||||

| 19 | CD | I | Select Control data or Display data for read/write operation. In S9 mode, CD pin is not used. Connect CD to VSS when not used. ”L”: Control data ”H”: Display data | |||||||||||||||||||||||||||||||||||||||||||||

| 20 | RST | I | When RST=”L”, all control registers are re-initialized by their default states. Since UC1608x has built-in Power-ON-Reset and Software Reset command, RST pin is not required for proper chip operation. When RST is not used, connect the pin to VDD. |

|||||||||||||||||||||||||||||||||||||||||||||

| 21 | CS | I | Chip Select. The chip is selected when CS=”H”. When the chip is not selected, D[7:0] will be high impedance. | |||||||||||||||||||||||||||||||||||||||||||||

| 22 | BM0 | I | Bus mode: The interface bus mode is determined by BM[1:0] and D[7:6] by the following relationship:

|

|||||||||||||||||||||||||||||||||||||||||||||

| 23 | BM1 |

通过点击「允许所有 Cookie」,代表您同意在您的设备上存储 Cookie 以增强网站浏览体验、分析网站使用情况并协助我们的营销和网站效能优化工作。您可以在我们的隐私权政策中找到有关于此的更多信息。