私たちはあなたのプライバシーを大切にします

「すべてのクッキーを許可」をクリックすると、サイトのナビゲーションを向上させ、サイト使用状況を分析し、マーケティングおよびパフォーマンスの取り組みを支援するために、クッキーをデバイスに保存することに同意したことになります。この件に関する詳細情報は、ポリシーをご覧ください。プライバシーポリシー

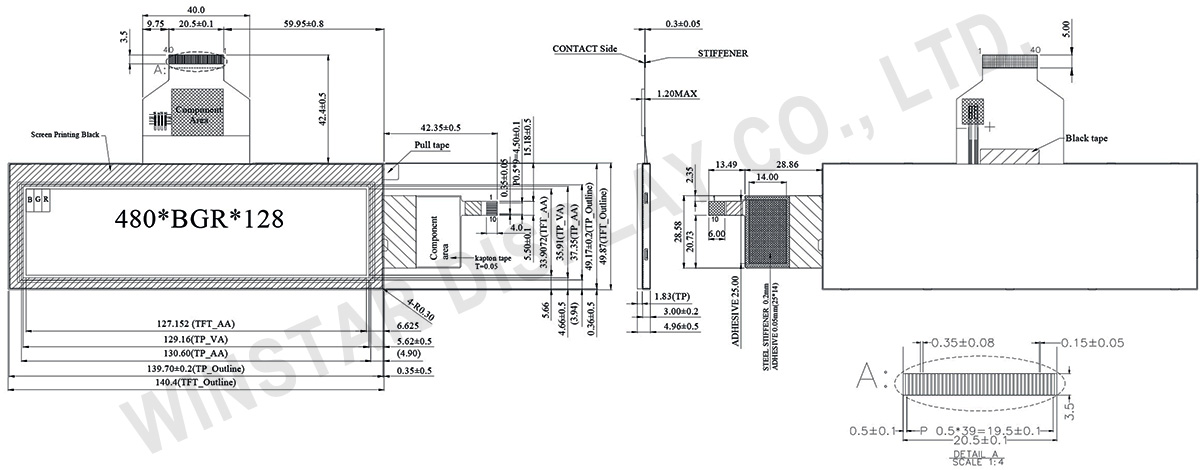

WF52BTIASDNG0 は、5 点マルチタッチ対応の静電容量式タッチパネルを備えた 5.2 インチバー型 TFT LCD モジュールです。トップビュー(12時方向)を特徴とし、480x128 ピクセルの高品質でカラフルな画像を提供します。本モジュールは、ST7252 または同等のドライバICを内蔵し、静電容量式タッチコントローラICは CYTMA568 です。SYNC モードで 24 ビット RGB パラレルインターフェースをサポートします。輝度は 400 ニット、コントラスト比は 500:1、視野角は 12 時方向、グレースケール反転方向は 6 時方向です。もしお客様がボトムビュー(6時方向)でグレースケール反転方向が 12時方向を必要とする場合は、WF52A モデルをお選びください。

LCM(VCC)の電源電圧範囲は 3.0V ~ 3.6V、標準値は 3.3V です。動作温度範囲は -20℃ ~ +70℃、保管温度範囲は -30℃ ~ +80℃ です。

| 項目 | 仕様 | 単位 |

|---|---|---|

| サイズ(対角線) | 5.2 | インチ |

| ドットマトリクス(解像度) | 480 x RGB x 128 | dots |

| モジュールサイズ | 140.4 x 49.87 x 4.96 | mm |

| アクティブエリア | 127.152 x 33.9072 | mm |

| ドットピッチ | 0.0883 x 0.2649 | mm |

| LCD タイプ | TFT・ノーマリ・ホワイト・透過型 | |

| 視野角 | 12時方向 | |

| グレースケール反転 | 6時方向 | |

| 画面アスペクト比 | バータイプ | |

| バックライトタイプ | LED・ノーマリ・ホワイト | |

| ドライバ IC | ST7252コントローラー内蔵或いは互換性IC | |

| インターフェース | RGB 24bit | |

| CTP IC | CYTMA568或いは互換性IC | |

| CTP FW バージョン | 0x0002 | |

| タッチパネルタイプ | 静電容量式タッチパネル (PCAP) | |

| 表面 | グレア | |

| 項目 | 記号 | 最小値 | 典型値 | 最大値 | 単位 |

|---|---|---|---|---|---|

| 動作温度 | TOP | -20 | - | +70 | ℃ |

| 貯蔵温度 | TST | -30 | - | +80 | ℃ |

| 項目 | 記号 | 最小値 | 典型値 | 最大値 | 単位 |

|---|---|---|---|---|---|

| LCM電源電圧 | VCC | 3.0 | 3.3 | 3.6 | V |

| タッチ電源電圧 | VDDT | 2.8 | - | 3.3 | V |

| LCM電源電流 | ICC | - | 20 | - | mA |

| パラメーター | 記号 | 最小値 | 典型値 | 最大値 | 単位 |

|---|---|---|---|---|---|

| LED電流 | - | 60 | - | mA | |

| LED電源 | VLED+ | 16.8 | 18.6 | 21 | V |

| LEDの寿命 | 50,000 | - | - | Hr |

| Pin | 記号 | 説明 |

|---|---|---|

| 1 | VLED- | Power for LED backlight cathode |

| 2 | VLED+ | Power for LED backlight anode |

| 3 | GND | Power ground |

| 4 | VCC | Power voltage |

| 5 | R0 | Red data (LSB) |

| 6 | R1 | Red data |

| 7 | R2 | Red data |

| 8 | R3 | Red data |

| 9 | R4 | Red data |

| 10 | R5 | Red data |

| 11 | R6 | Red data |

| 12 | R7 | Red data (MSB) |

| 13 | G0 | Green data (LSB) |

| 14 | G1 | Green data |

| 15 | G2 | Green data |

| 16 | G3 | Green data |

| 17 | G4 | Green data |

| 18 | G5 | Green data |

| 19 | G6 | Green data |

| 20 | G7 | Green data (MSB) |

| 21 | B0 | Blue data (LSB) |

| 22 | B1 | Blue data |

| 23 | B2 | Blue data |

| 24 | B3 | Blue data |

| 25 | B4 | Blue data |

| 26 | B5 | Blue data |

| 27 | B6 | Blue data |

| 28 | B7 | Blue data (MSB) |

| 29 | GND | Power ground |

| 30 | CLK | Pixel clock (DCLK) |

| 31 | LR | Right /Left selection; Default R/L is Pull High |

| 32 | HSYNC | Horizontal sync signal; negative polarity |

| 33 | VSYNC | Vertical sync signal; negative polarity |

| 34 | NC | No connection |

| 35 | UD | Up/down selection; Default U/D is Pull High |

| 36 | RESET | Reset signal |

| 37 | NC | No connection |

| 38 | NC | No connection |

| 39 | NC | No connection |

| 40 | NC | No connection |

| Pin | 記号 | 説明 |

|---|---|---|

| 1 | VSS | Ground for analog circuit |

| 2 | VDDT | Power Supply : +3.3V |

| 3 | SCL | I2C clock signal |

| 4 | NC | No connect |

| 5 | SDA | I2C data signal |

| 6 | NC | No connect |

| 7 | RST | External reset signal, active low |

| 8 | NC | No connect |

| 9 | INT | Interrupt signal, active low, asserted to request Host start a new transcation. |

| 10 | VSS | Ground for analog circuit |

「すべてのクッキーを許可」をクリックすると、サイトのナビゲーションを向上させ、サイト使用状況を分析し、マーケティングおよびパフォーマンスの取り組みを支援するために、クッキーをデバイスに保存することに同意したことになります。この件に関する詳細情報は、ポリシーをご覧ください。プライバシーポリシー