우리는 귀하의 프라이버시를 소중히 여깁니다

"모든 쿠키 허용"을 클릭하면 사이트 탐색을 개선하고, 사이트 사용을 분석하며, 마케팅 및 성능 노력에 도움을 주기 위해 쿠키를 귀하의 장치에 저장하는 데 동의한 것으로 간주됩니다. 이 주제에 대한 추가 정보는 당사의 정책에서 확인할 수 있습니다. 개인정보 보호정책

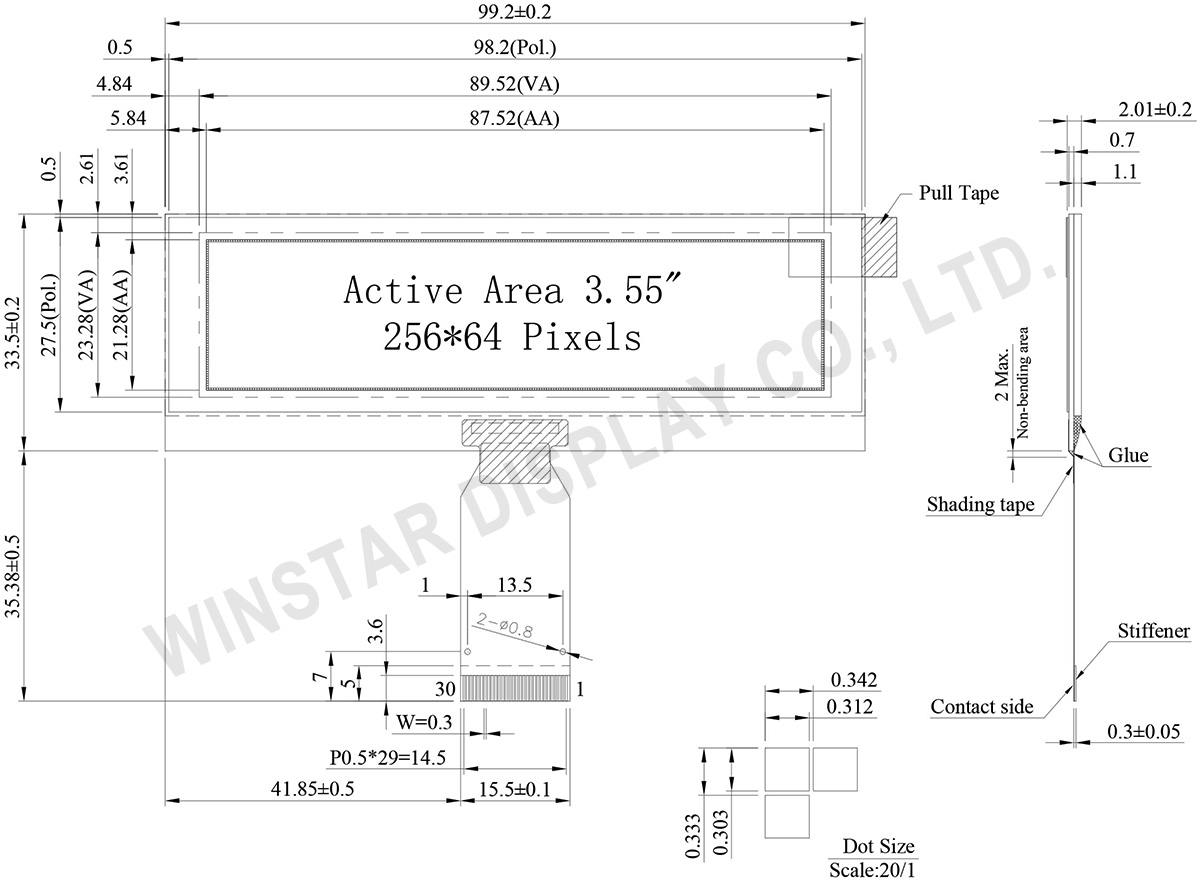

WEO025664D는 3.55인치 COG 구조의 그래픽 OLED 디스플레이로, 256×64 도트 매트릭스와 SSD1322 컨트롤러 IC를 내장하고 있습니다. 4비트(16단계) 그레이스케일을 지원하며, 6800/8080 병렬 인터페이스와 3선/4선 SPI 등 다양한 호스트 인터페이스 옵션을 제공합니다. OLED는 높은 명암비와 넓은 시야각을 제공하여 다양한 조명 환경에서도 안정적인 가독성을 보장합니다.

이 모델은 3.3V 논리 전원과 16V 디스플레이 구동 전압으로 동작합니다. 50% 체커보드 패턴에서의 전류 소모는 전형적으로 35mA(VCC=16V)이며, 모듈은 1/64 듀티 드라이브 방식을 사용합니다.

WEO025664D는 장기적으로 안정적인 디스플레이가 필요한 장비에 적합하며, 의료기기, 제어 패널, 셀프 계산대, 티켓 발권기 및 주차 요금 징수기 등에 사용 가능합니다. 동작 온도 범위는 –40°C ~ +80°C, 저장 온도 범위는 –40°C ~ +85°C입니다.

| 항목 | 치수 | 단위 |

|---|---|---|

| 도트 매트릭스 | 256 x 64 | - |

| 모듈 치수 | 99.2 × 33.5 × 2.01 | mm |

| 활성 영역 | 87.52 × 21.28 | mm |

| 도트 크기 | 0.312 × 0.303 | mm |

| 도트 피치 | 0.342 × 0.333 | mm |

| 디스플레이 모드 | 패시브 매트릭스 | |

| 디스플레이 색상 | Monochrome | |

| Drive Duty | 1/64 Duty | |

| 그레이스케일 | 4 bits | |

| IC | SSD1322 | |

| 인터페이스 | 6800, 8080, SPI | |

| 크기 | 3.55 인치 | |

| Parameter | 기호 | 최소값 | 최대값 | 단위 |

|---|---|---|---|---|

| Supply Voltage for Logic | VDD | -0.5 | 2.75 | V |

| Low voltage power supply | VCI | -0.3 | 4 | V |

| Supply Voltage for I/O Pins | VDDIO | -0.5 | VCI | V |

| Supply Voltage for Display | VCC | -0.5 | 20 | V |

| 작동 온도 | TOP | -40 | 80 | °C |

| 보관 온도 | TSTG | -40 | 85 | °C |

| 항목 | 기호 | 조건 | 최소값 | 대표값 | 최대값 | 단위 |

|---|---|---|---|---|---|---|

| Low Voltage power supply | VCI | - | 2.4 | 3.3 | 3.5 | V |

| Supply Voltage for Display | VCC | - | 10.0 | 16.0 | 16.5 | V |

| Logic supply voltage | VDD | - | 2.4 | - | 2.6 | V |

| Power for I/O pins | VDDIO | - | 1.65 | VCI | V | |

| High Level Input | VIH | - | 0.8×VDDIO | - | VDDIO | V |

| Low Level Input | VIL | - | 0 | - | 0.2×VDDIO | V |

| High Level Output | VOH | - | 0.9×VDDIO | - | VDDIO | V |

| Low Level Output | VOL | - | 0 | - | 0.1×VDDIO | V |

| Display 50% Pixel on | VCC =16 V | - | - | 35 | 55 | mA |

| Pin Number | 기호 | I/O | 기능 | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | ESD_GND | P | Ground | ||||||||||

| 2 | VSS | P | Ground. | ||||||||||

| 3 | VCC | P | Power supply for panel driving voltage. This is also the most positive power voltage supply pin. |

||||||||||

| 4 | VCOMH | P | COM signal deselected voltage level. A capacitor should be connected between this pin and VSS. |

||||||||||

| 5 | VLSS | P | Analog system ground pin. | ||||||||||

| 6~13 | D7~D0 | I/O | Host Data Input/Output Bus These pins are 8-bit bi-directional data bus to be connected to the microprocessor’s data bus. When serial mode is selected, D1 will be the serial data input SDIN and D0 will be the serial clock input SCLK. |

||||||||||

| 14 | E/RD# | I | Read/Write Enable or Read This pin is MCU interface input. When interfacing to a 68XX-series microprocessor, this pin will be used as the Enable (E) signal. Read/write operation is initiated when this pin is pulled high and the CS# is pulled low. When connecting to an 80XX-microprocessor, this pin receives the Read (RD#) signal. Data read operation is initiated when this pin is pulled low and CS# is pulled low. When serial mode is selected, this pin must be connected to VSS. |

||||||||||

| 15 | R/W# | I | Read/Write Select or Write This pin is MCU interface input. When interfacing to a 68XX-series microprocessor, this pin will be used as Read/Write (R/W#) selection input. Pull this pin to “High” for read mode and pull it to “Low” for write mode. When 80XX interface mode is selected, this pin will be the Write (WR#) input. Data write operation is initiated when this pin is pulled low and the CS# is pulled low. When serial mode is selected, this pin must be connected to VSS. |

||||||||||

| 16 | BS0 | I | Communicating Protocol Select These pins are MCU interface selection input. See the following table:

Note (1) 0 is connected to VSS (2) 1 is connected to VDDIO |

||||||||||

| 17 | BS1 | ||||||||||||

| 18 | D/C# | I | Data/Command Control This pin is Data/Command control pin connecting to the MCU. When the pin is pulled HIGH, the content at D[7:0] will be interpreted as data. When the pin is pulled LOW, the content at D[7:0] will be interpreted as command. |

||||||||||

| 19 | CS# | I | Data/Command Control This pin is the chip select input connecting to the MCU. The chip is enabled for MCU communication only when CS# is pulled LOW. |

||||||||||

| 20 | RES# | I | This pin is reset signal input. When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation. |

||||||||||

| 21 | FR | O | This pin is No Connection pins. Nothing should be connected to this pin. This pin should be left open individually. | ||||||||||

| 22 | IREF | I | Current Reference for Brightness Adjustment This pin is segment current reference pin. A resistor should be connected between this pin and VSS. Set the current lower than 10uA. |

||||||||||

| 23 | N.C. | - | Reserved Pin The N.C. pin between function pins are reserved for compatible and flexible design. |

||||||||||

| 24 | VDDIO | P | Power Supply for I/O Pin It should be matched with the MCU interface voltage level. |

||||||||||

| 25 | VDD | P | Power Supply for Core Logic Circuit Power supply pin for core logic operation. A capacitor is required to connect between this pin and VSS |

||||||||||

| 26 | VCI | P | Power Supply for Operation VCI must always be equal to or higher than VDD and VDDIO. |

||||||||||

| 27 | VSL | P | Voltage Output Low Level for SEG Signal This is segment voltage reference pin. When external VSL is not used, this pin should be left open. When external VSL is used, this pin should connect with resistor and diode to ground. |

||||||||||

| 28 | VLSS | P | Ground of Analog Circuit These are the analog ground pins. They should be connected to VSS externally. |

||||||||||

| 29 | VCC | P | Power Supply for OLED Panel These are the most positive voltage supply pin of the chip. They must be connected to external source. |

||||||||||

| 30 | ESD GND | P | Ground |

"모든 쿠키 허용"을 클릭하면 사이트 탐색을 개선하고, 사이트 사용을 분석하며, 마케팅 및 성능 노력에 도움을 주기 위해 쿠키를 귀하의 장치에 저장하는 데 동의한 것으로 간주됩니다. 이 주제에 대한 추가 정보는 당사의 정책에서 확인할 수 있습니다. 개인정보 보호정책