Module LCD, Afficheur PMOLED, Fabricants LCD

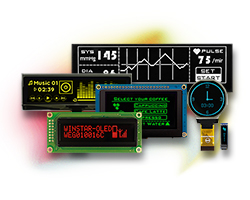

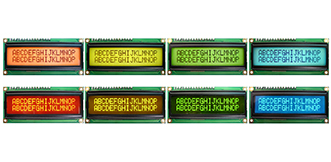

WINSTAR offre un vaste choix d’afficheurs LCD ou PMOLED industriels standards, sur-mesure, complets ou partiels. Nous proposons des modules LCD alphanumériques ou graphiques en monochrome TN/STN/FSTN, des solutions de modules COG, FSC-LCD, VATN, des afficheurs TFT ainsi que des modules PMOLED. Afin d’offrir le support technique qui convient à toute cette gamme, les équipes techniques de WINSTAR sont là pour aider les clients à construire le produit complet incluant les différents accessoires (claviers, dalles tactiles, connecteurs ZIF, FPC…). WINSTAR propose également des cartes de tests adaptées pour vérifier les fonctionnalités des produits. Aujourd’hui, WINSTAR Embedded System offre également un support technique pour les solutions d’informatique industrielle entre écran TFT et cartes mères.